English PALLETS Channel

Delivering technical videos of FPGA & analog parts such as Xilinx & Bellnix & Linear Technology

Click here for YouTube Page

|

For those who use Xilinx Vivado® Design Suite for the first time |

|

Overview Xilinx Development Tool ・4 HW Development ・Vivado® Design Suite,SDK,HLS,SDSoC™ |

|

How to use Vivado® Design Suite ① Create Project ・Resignate FPGA type and evaluation board and introduce how to create a project |

|

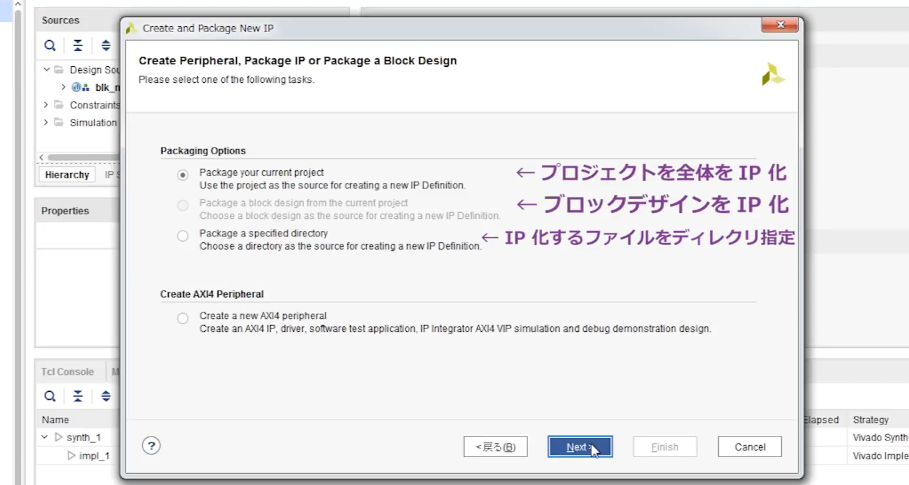

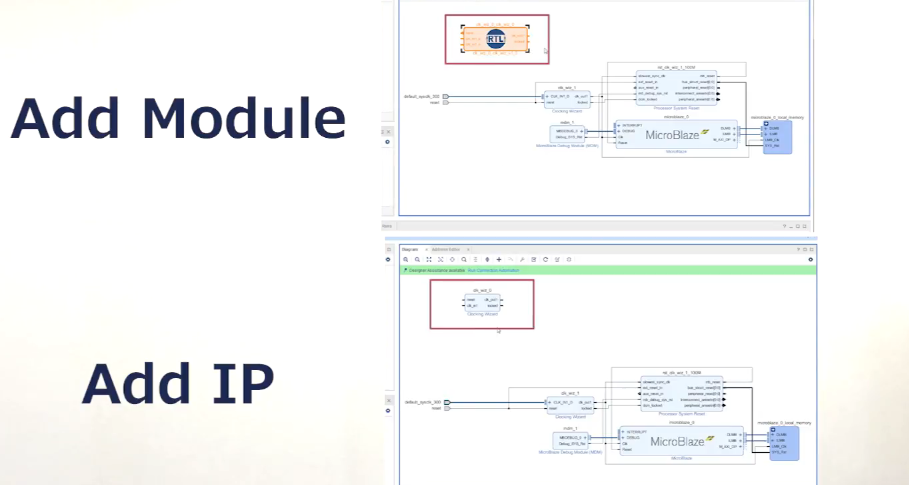

How to use Vivado® Design Suite ② Generate IP ・IP generation method and RTL IP conversion method |

|

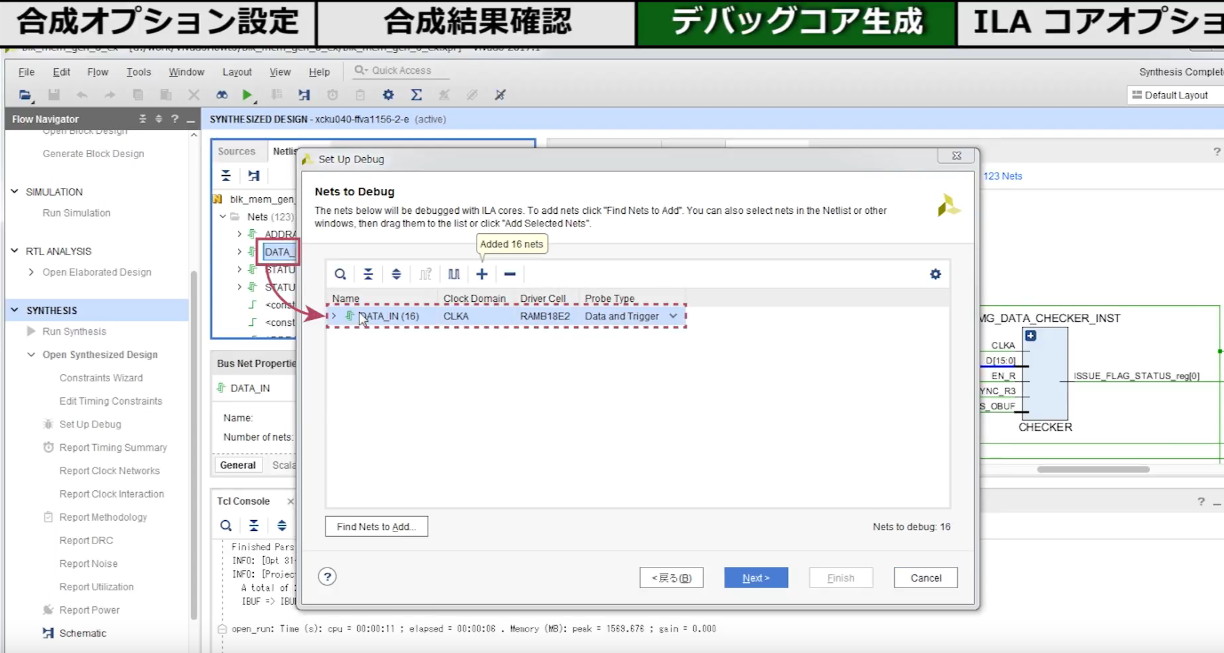

How to use Vivado® Design Suite ③ Synthesis and Debug Core Generation ・Logic Synthesis Option ・Debug core generation method without RTL description |

|

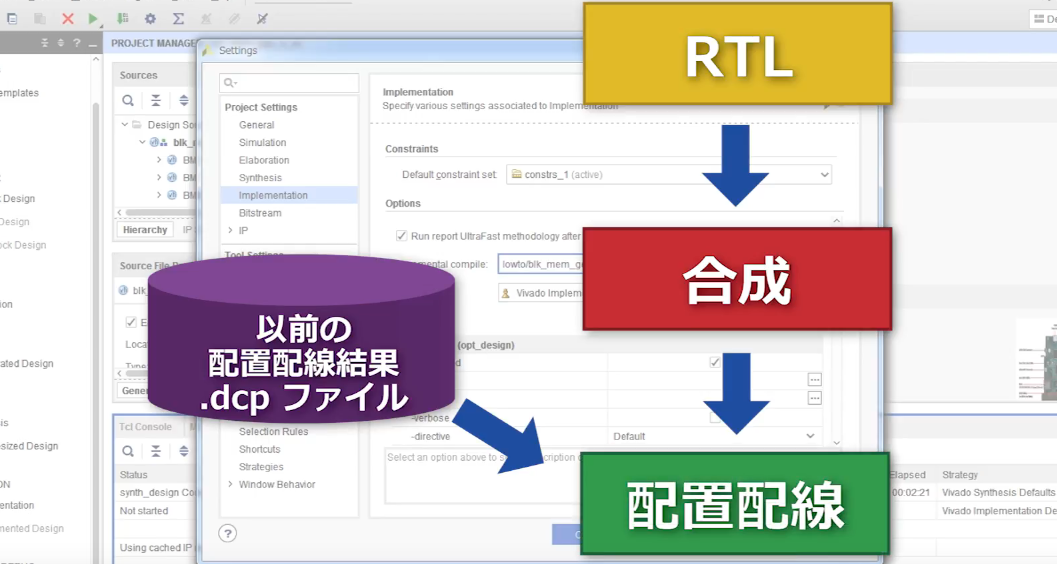

How to use Vivado® Design Suite ④ Implement ・Incremental compilation ・Placement and routing option setting |

|

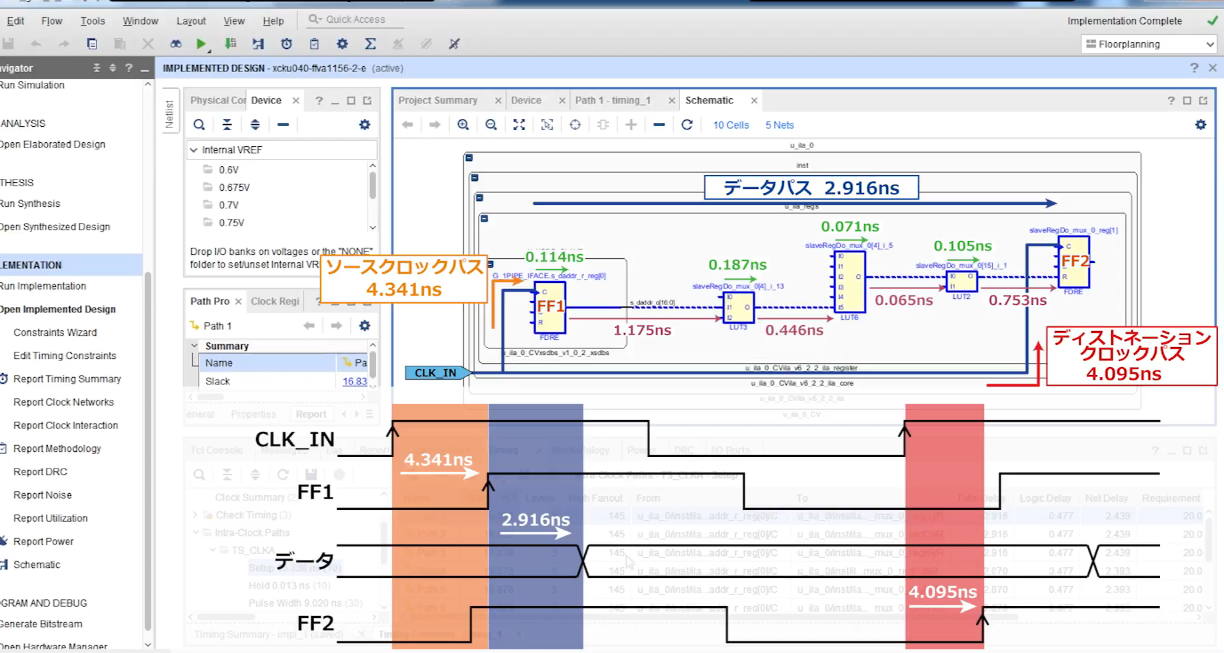

How to use Vivado® Design Suite ⑤ Timing summary report ・Timing summary report output |

|

How to use Vivado® Design Suite ⑥ Program & Debug ・Generate file to write on FPGAs |

|

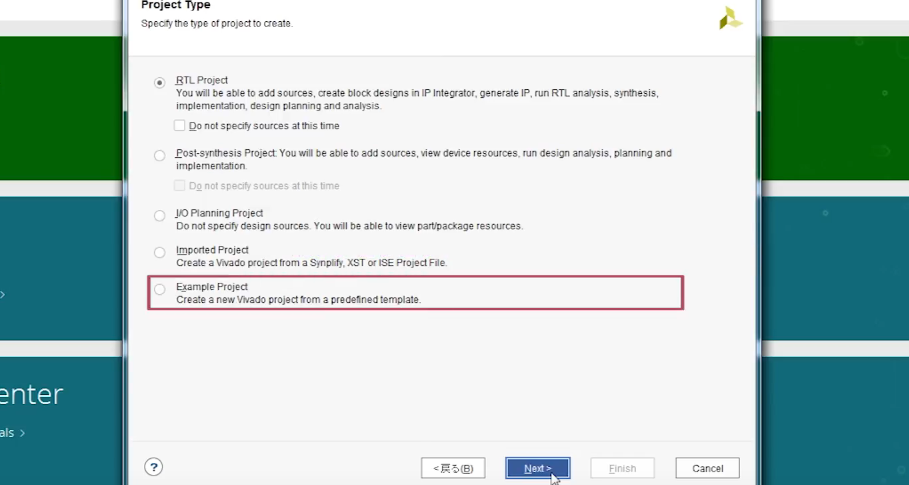

Example Design ・How to generate sample design |

|

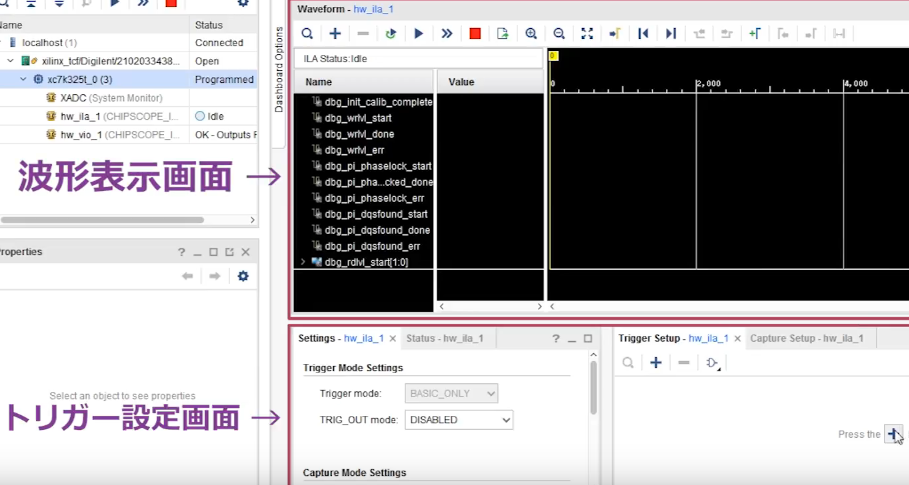

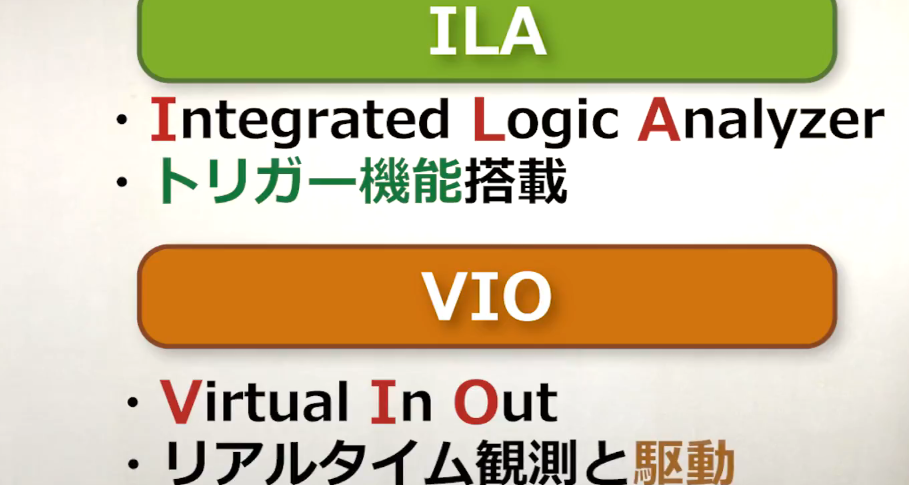

ILA VIO Tutorial ・You can check the internal operation of the FPGA and use it for debugging. |

|

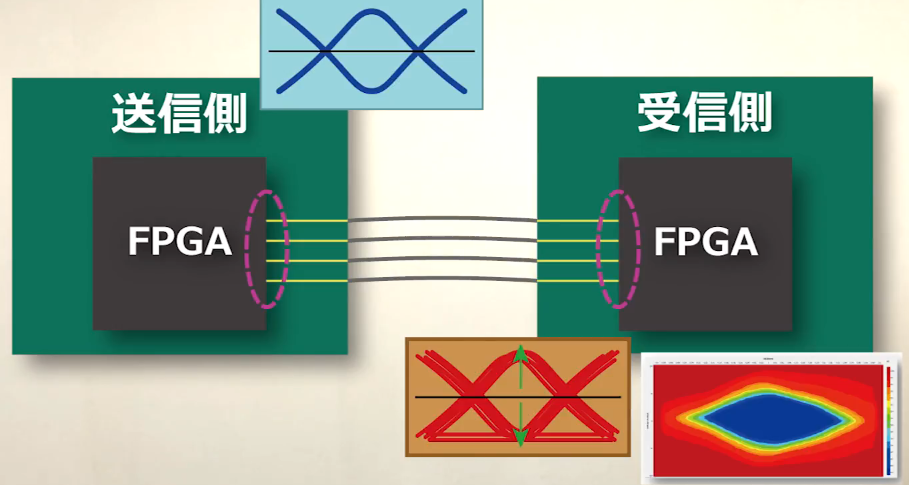

IBERT Tutorial ・We would like to introduce IBERT, debug IP of Transceiver. |

|

Xilinx Videos when creating schematics |

|

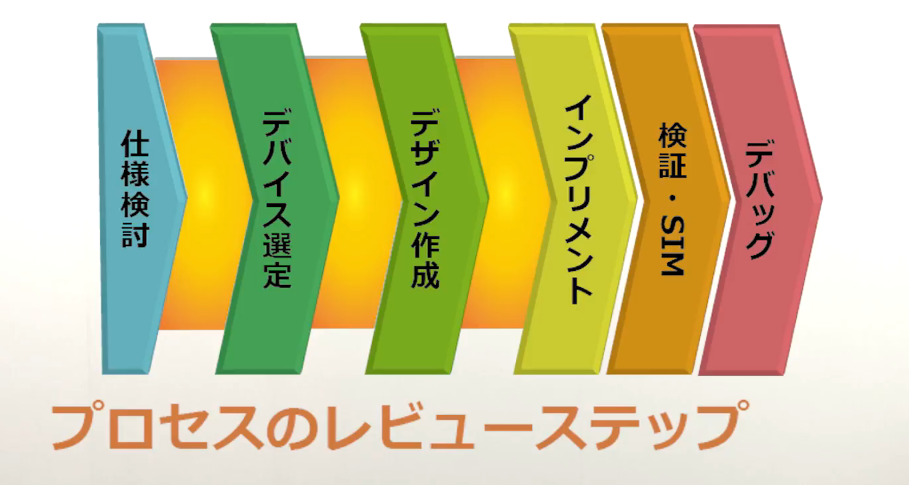

UltraFast™ Design Methodlogy ・A method to reduce backtracking man-hours by providing a review step for each process |

|

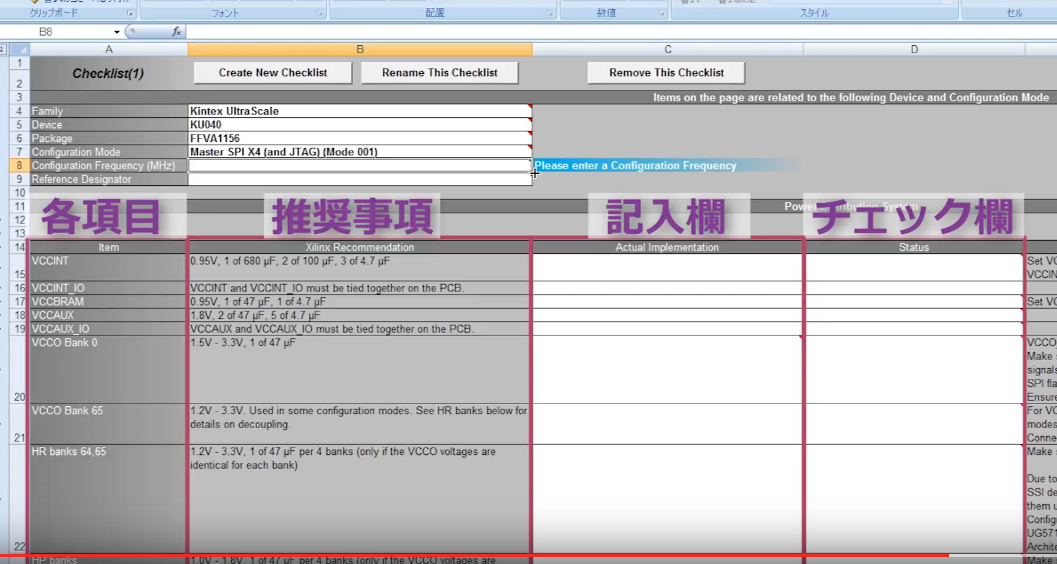

Schematics Review Sheet from UltraFast™ Design Methodlogy ・Schematics Review Sheet is prepared and it can be downloaded from the user guide UG949. |

|

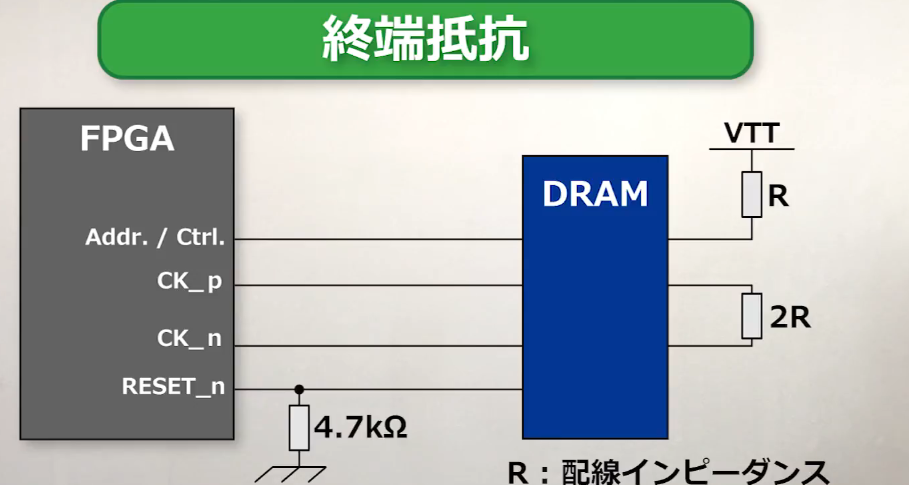

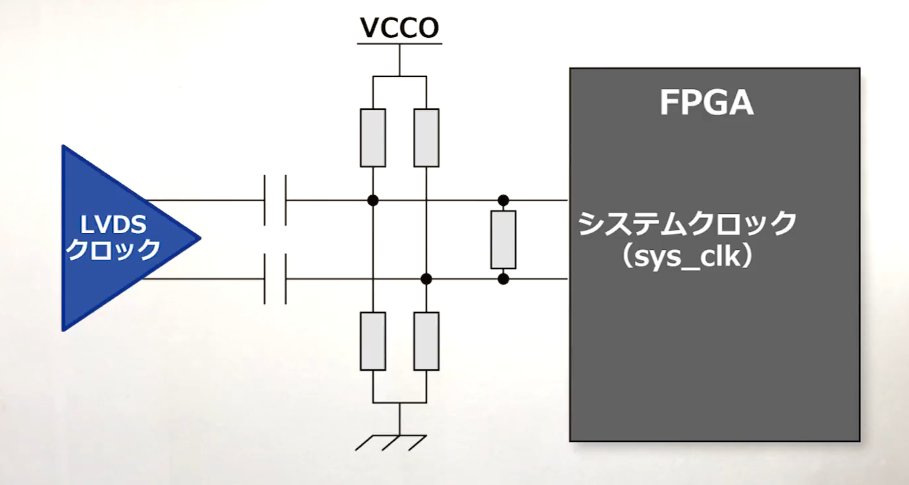

Schematics Check Point of 7 series MIG ・Question of Clock and Ternination for 7 series MIG |

|

Schematics Check Point of UltraScale™ MIG ・Question of Clock and Ternination forUltraScale™ MIG |

|

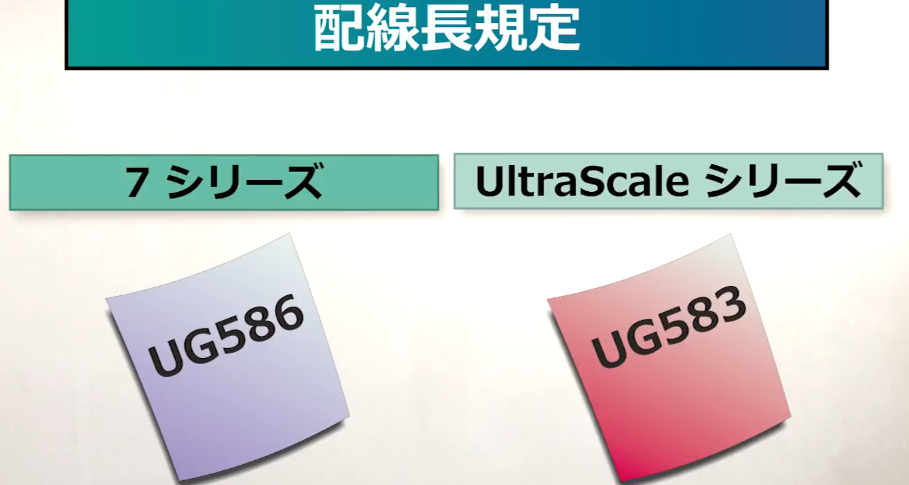

MIG Trace Length Requirements ・We observe the regulations, and a safe and secure interface. |

|

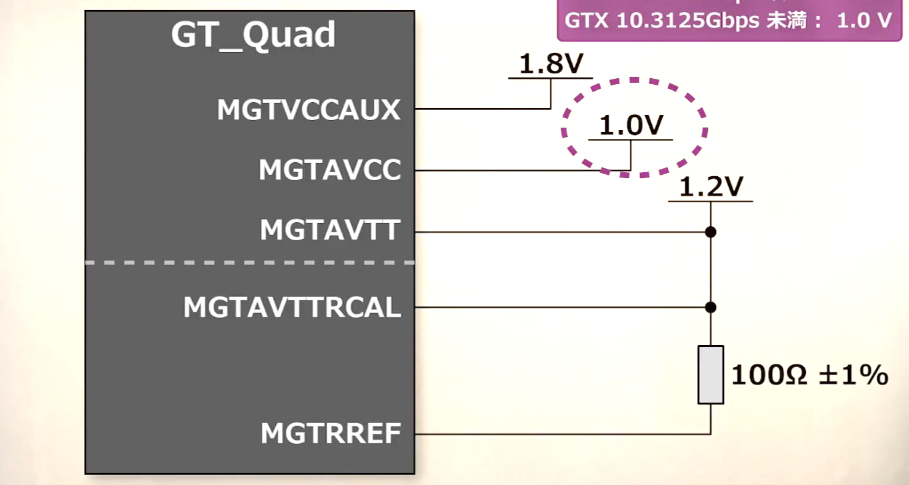

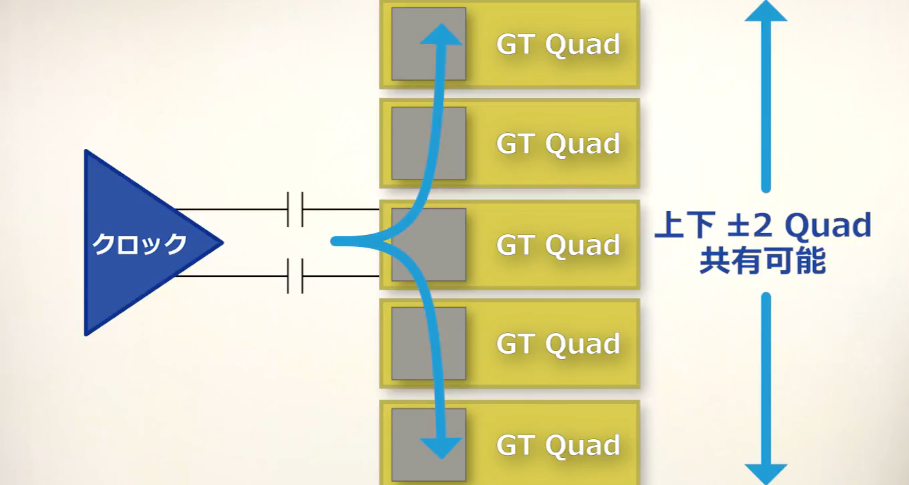

Schematics Check Point of 7 series Transceiver ・Introduction of clock circuit configuration, sharing width, connection method of power supply related pins |

|

Schematics Check Point of UltraScale™ series Transceiver ・Introduction of clock circuit configuration, sharing width, connection method of power supply related pins |

|

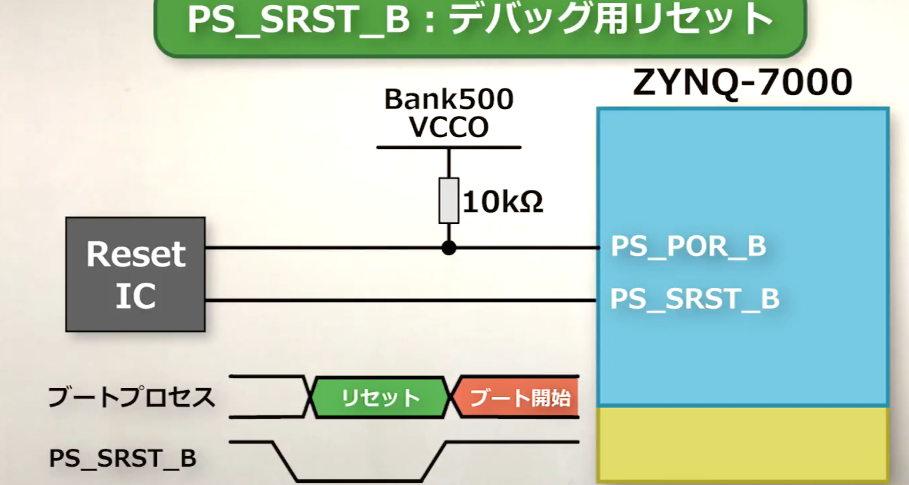

Schematics Check Point of Zynq®-7000 All Programmable SoC PS ・We would like to introduce Schematics of Zynq-7000 PS. |

|

FAQ of Xilinx |

|

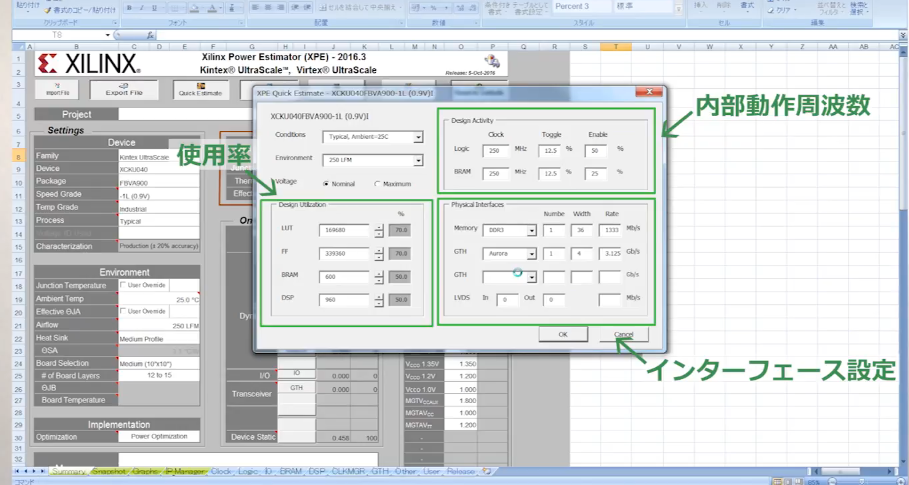

Estimate Power Consumption XPE ・You can estimate Power Consumption without crerating design. |

|

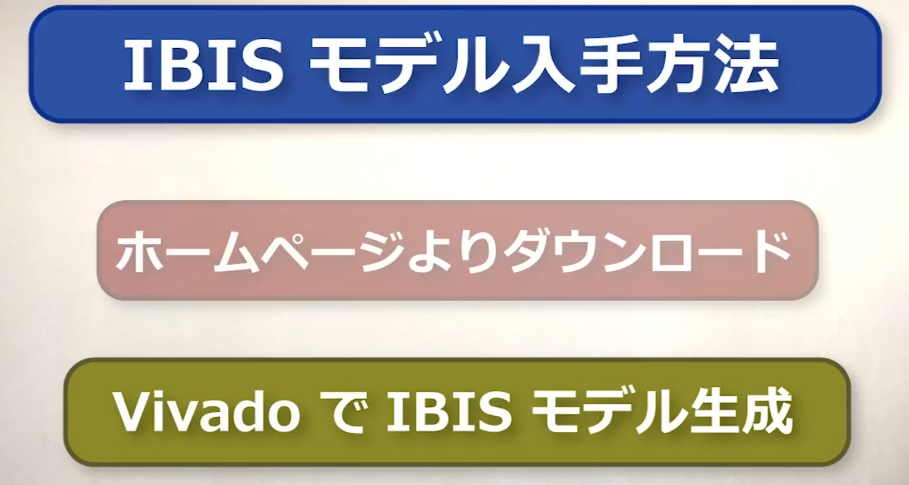

How to get IBIS model ・We would like to introduce how to get IBIS-model. |

|

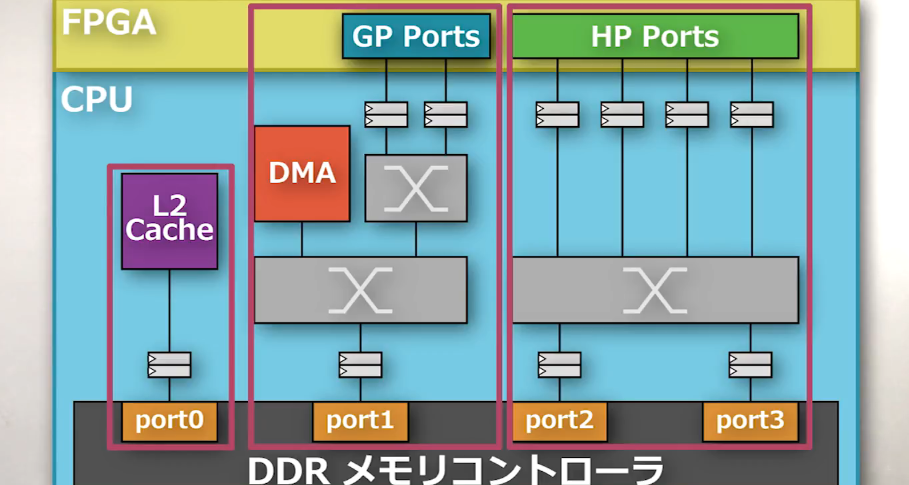

DDR Arbitration of Zynq®-7000 All Programmable SoC ・How to setting Arbitration of DDR Controller. |

|

Evaluation Kit Initial Operation Check, KC705 ・Xilinx has a Built-in Self Test (BIST) program, |

|

Xilinx Vivado® Design Suite License |

|

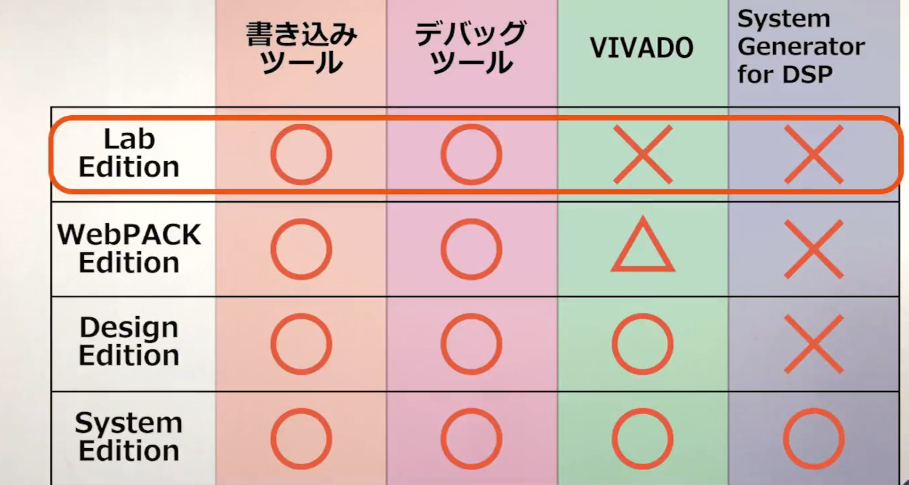

Vivado® Design Suite Edition & License ・We would like to introduce 4 FAQs of Vivado Design Suite License. |

|

How to set Node-Locked license ・We would like to introduce how to set up Node-Locked license. |

|

We would like to introduce how to set up Vivado Floating license. ・We would like to introduce how to set up Floating license. |

|

FAQ of VivadoR Design Suite License ・FAQs of Vivado® Design Suite license |

|

Xilinx Vivado® Design Suite 2017.1 |

|

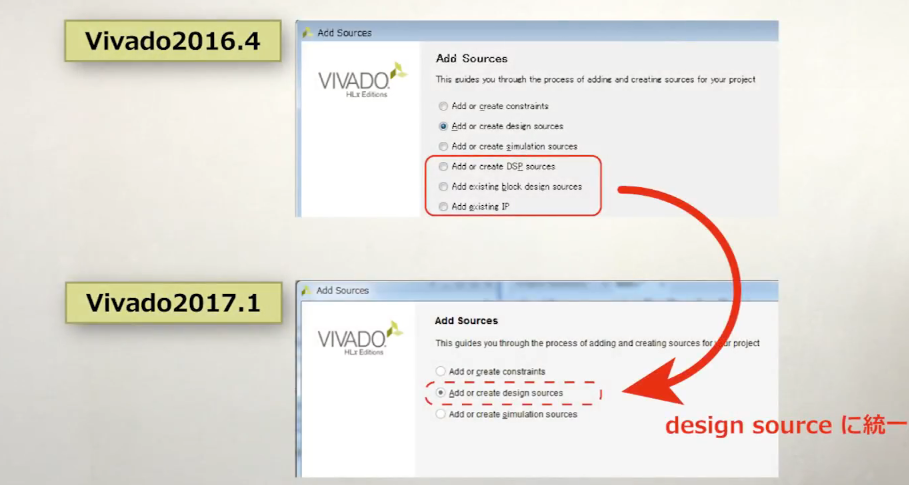

① Development Environment ・We would like to introduce what's new in Vivado2017.1. Part 1 is about development environment. |

|

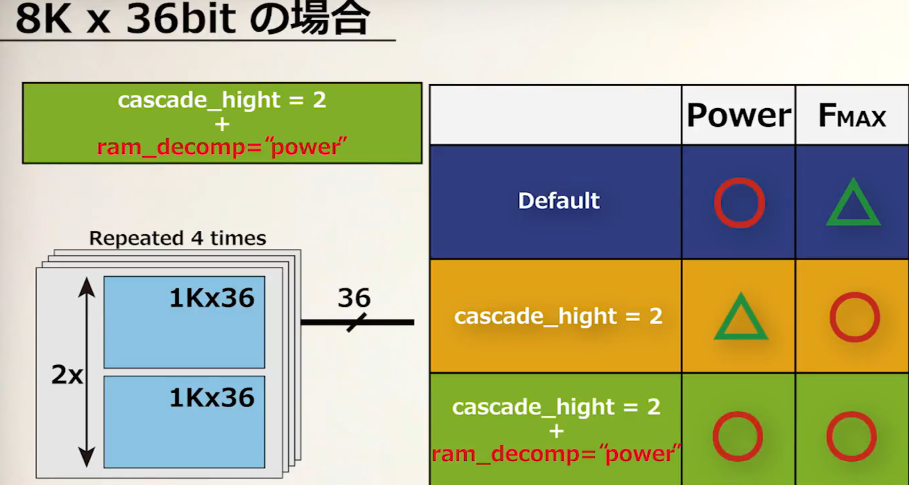

② Implementation ・More optimize options and improve compiler. |

|

③ Integration ・We would like to introduce what's new in Vivado2017.1. Part 3 is about Integration. |

|

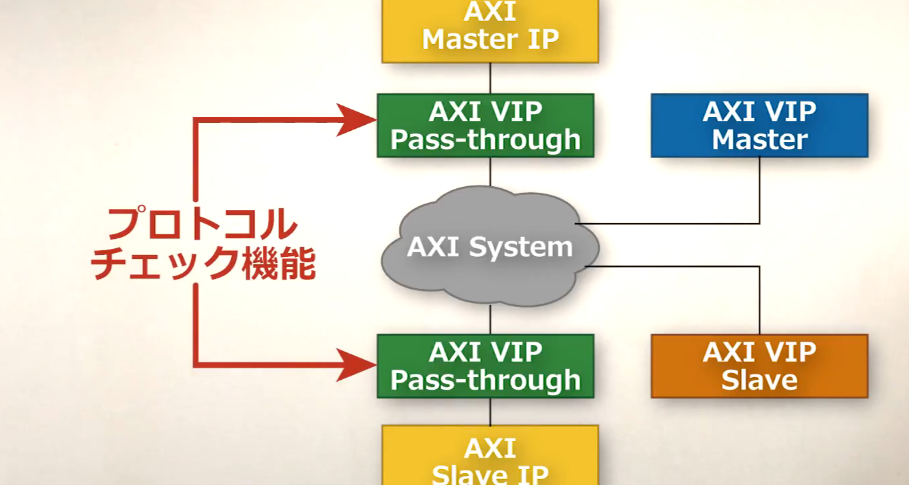

④ AXI Verification IP ・AXI Verification IP is instead of AXI BFM. |

|

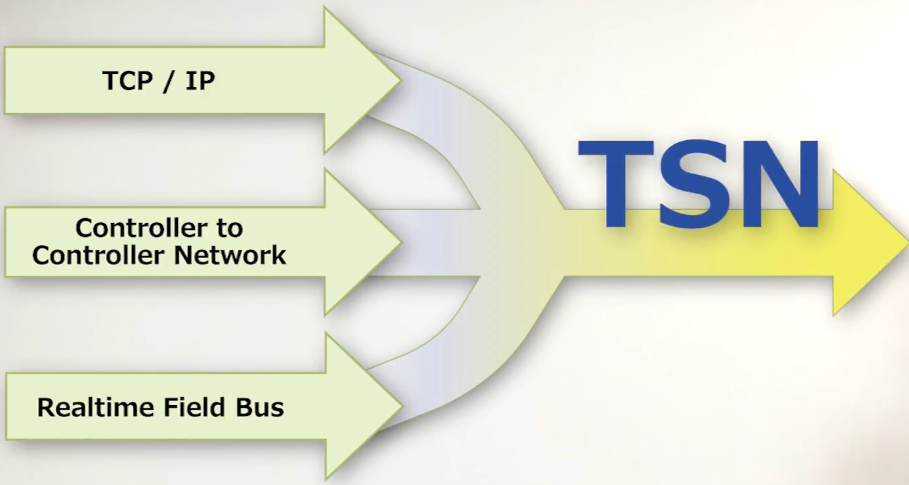

⑤ TSN IP ・Time Sensitive Network IP |

|

Xilinx Products |

|

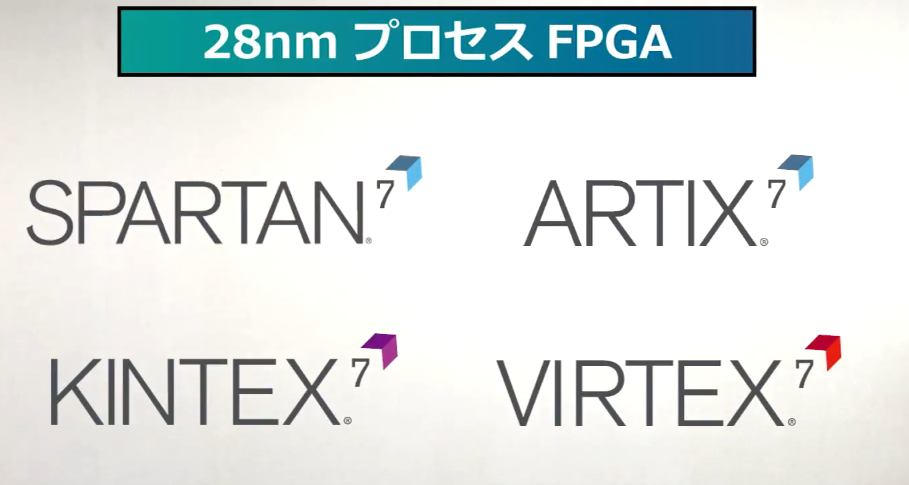

7 series FPGAs ・We introduce new product, Spartan 7. |

|

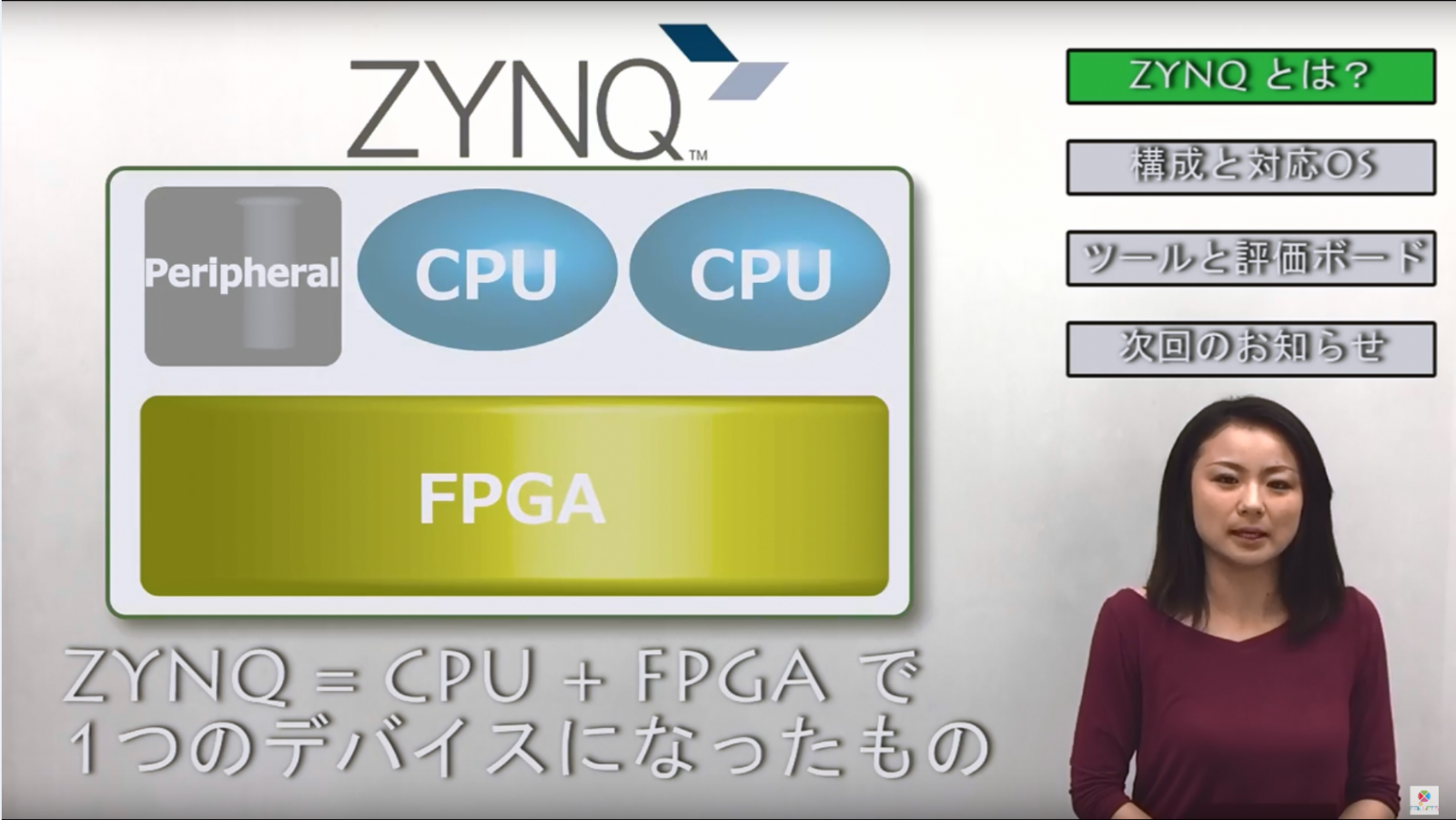

Zynq®-7000 All Programmable SoCs ・We introduce Zynq®-7000 All Programmable S |

|

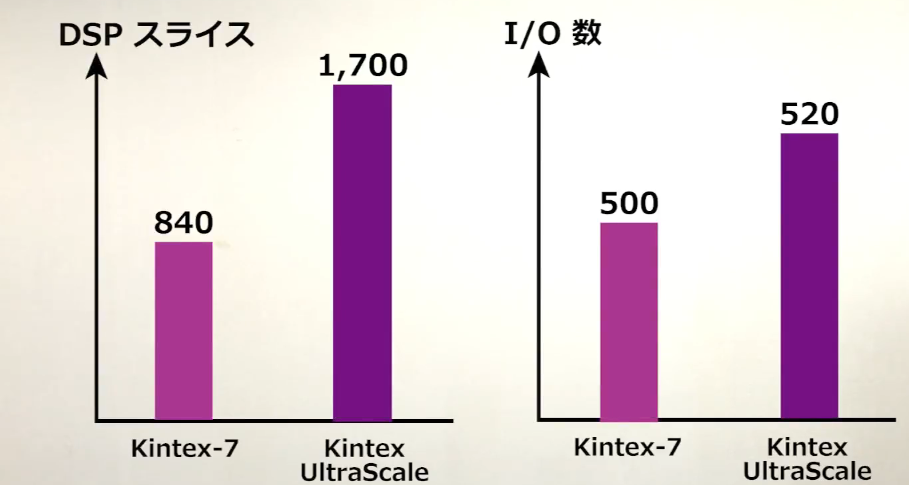

UltraScale™ FPGAs ・We introduce UltraScale™ series |

|

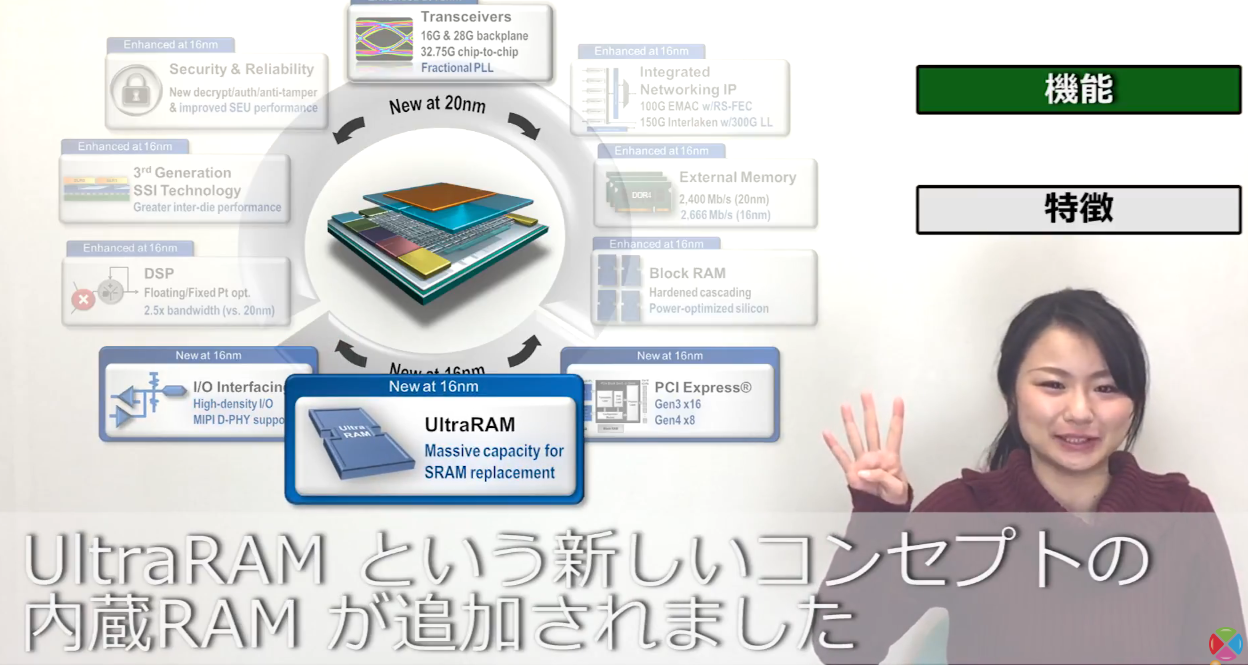

UltraScale+™ FPGA 紹介 ・We introduce UltraScale+™ series |

|

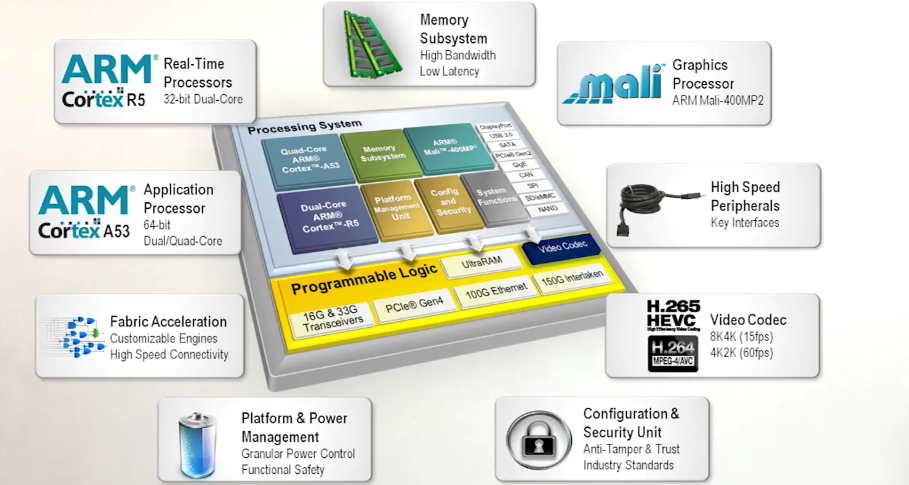

Zynq® UltraScale+™ MPSoCs ・We introduce Zynq UltraScale+™ MPSoCs |

|

Xilinx Zynq® series |

|

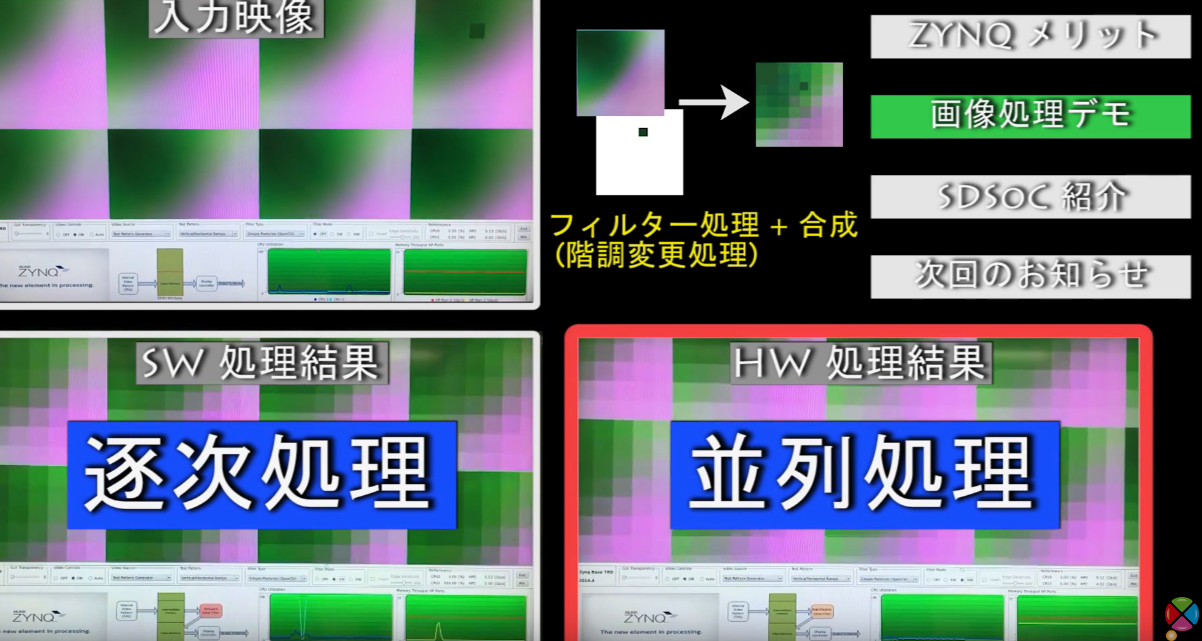

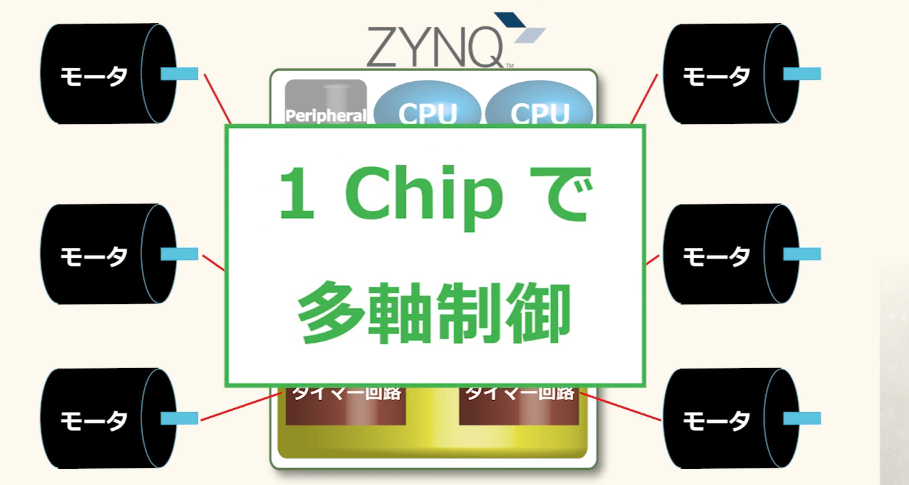

Zynqq®-7000 All Programmable SoC Benefit ・Advantage of Zynq is Hardware acceleration. |

|

First time for Zynq®-7000 All Programmable SoC This video is an interview of engineer who design with Zynq®-7000 All Programmable SoC |

|

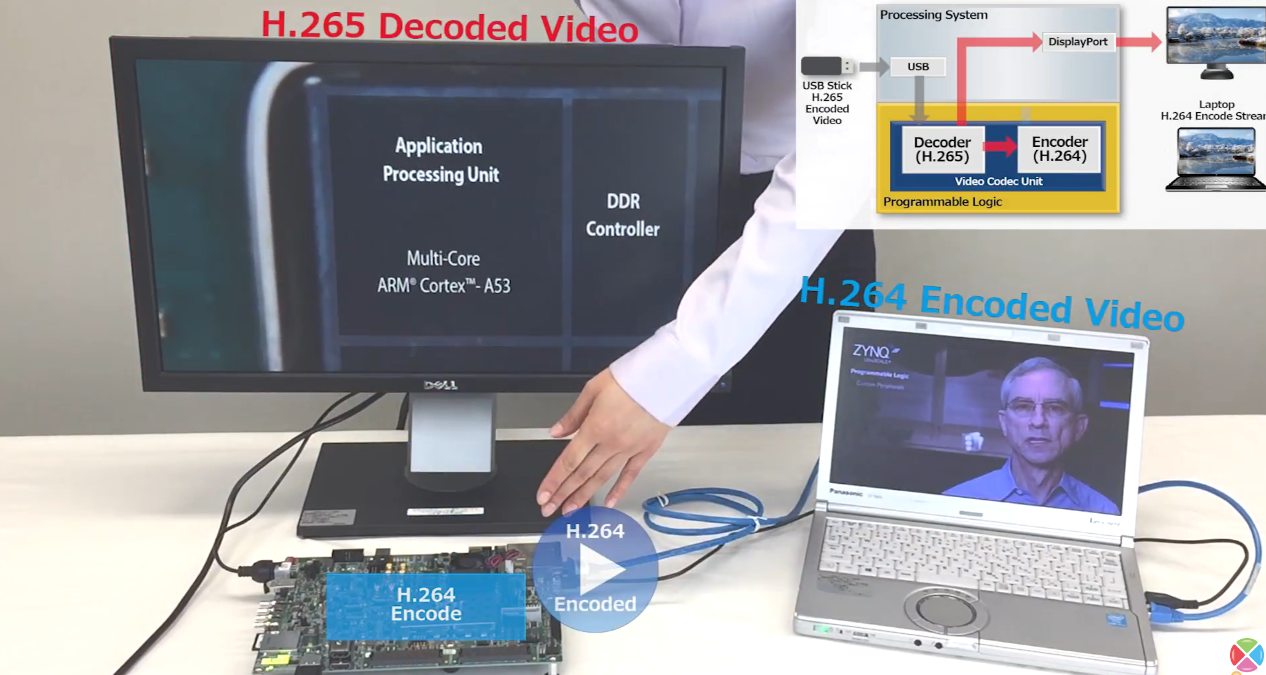

H.265 / H.264 Simultaneous Encode Decode Demonstration ・ZCU106 board is only a few in the world, This video is special video that can only be seen here !! |

|

Xilinx reVISION Stack |

|

① Machine Learning ・At first we talk about Machine Learning. |

|

② Advantage of FPGA with Machine Learning ・About advantage of FPGA with Machine Learning. |

|

Linear Technology LTspice |

|

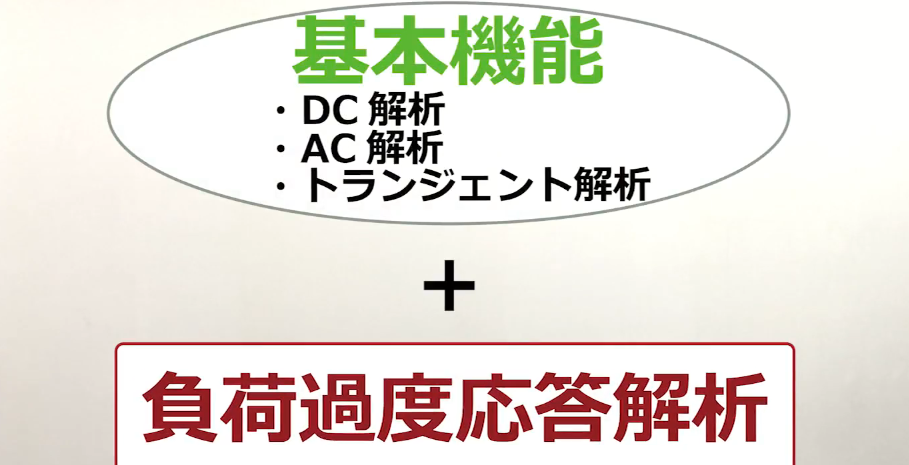

LTspice Overview ・Although LTspice is free, but multifunction !! |

|

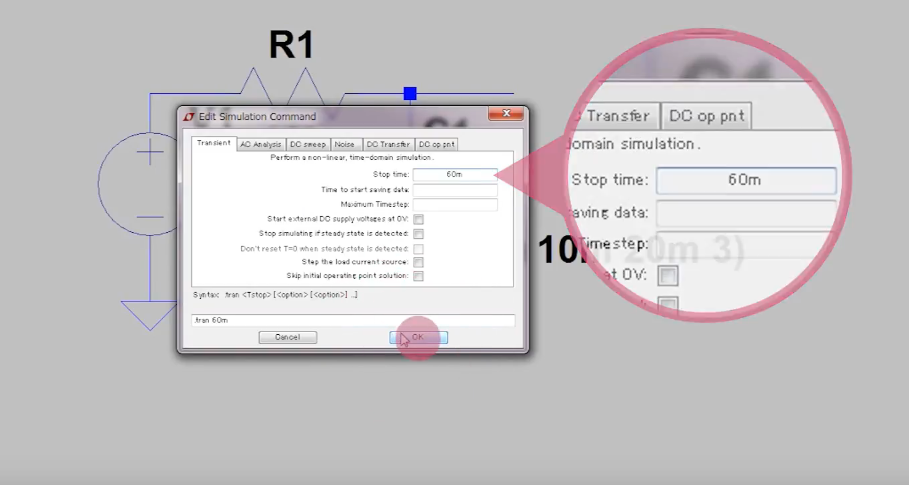

LTspice Operation ・From "Schematics input" to "Select parts", "Simulation". |

|

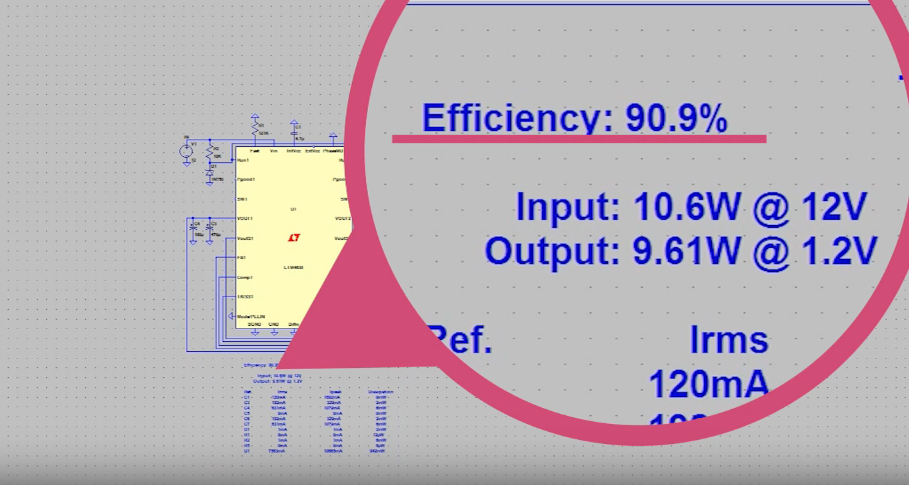

LTspice Efficiency Measurement ・We would like to introduce how to calculate power efficeincy. |

|

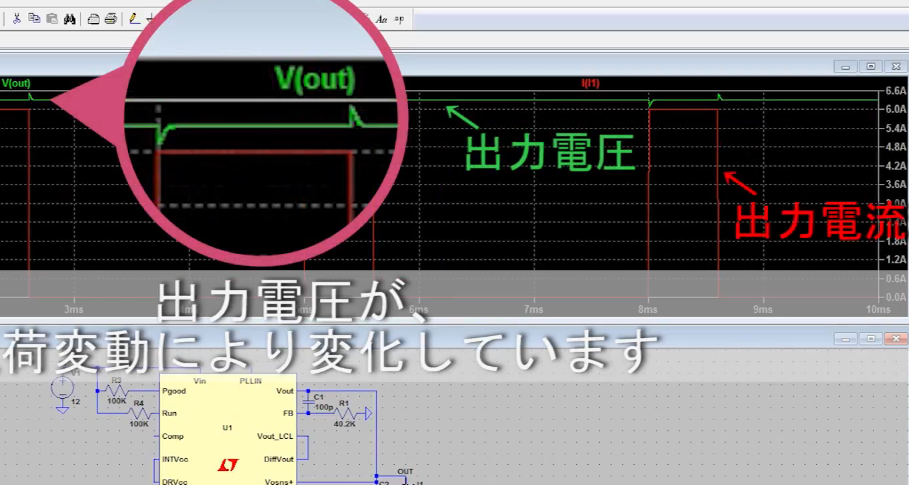

LTspice Load Transient Response Simulation ・For FPGA power supply design, load transient response is an important characteristic. |

|

Linear Technology Products |

|

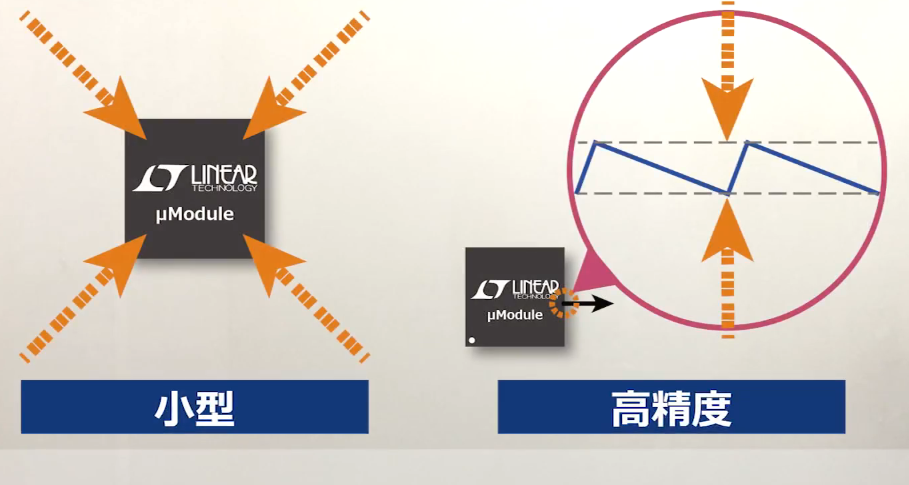

μModule Despite built-in inductor, it realizes a small package. |

|

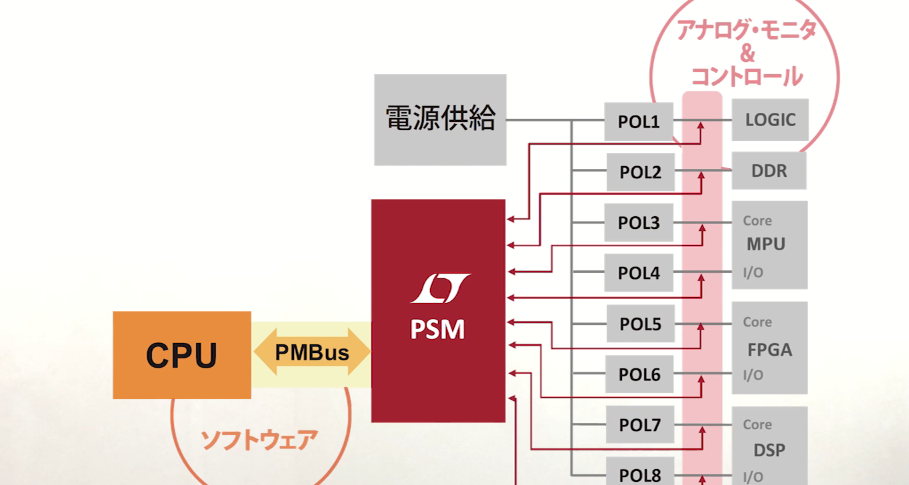

Power System Management PSM (Power System Management) PSM can control other power supply. Realize ±0.25% accuracy, and control power sequence. |

|

Bellnix Prodcuts |

|

Bellnix Wireless power supply This system adopted original architecture of transformer, it will make high power efficiency on your sysytem. |

|

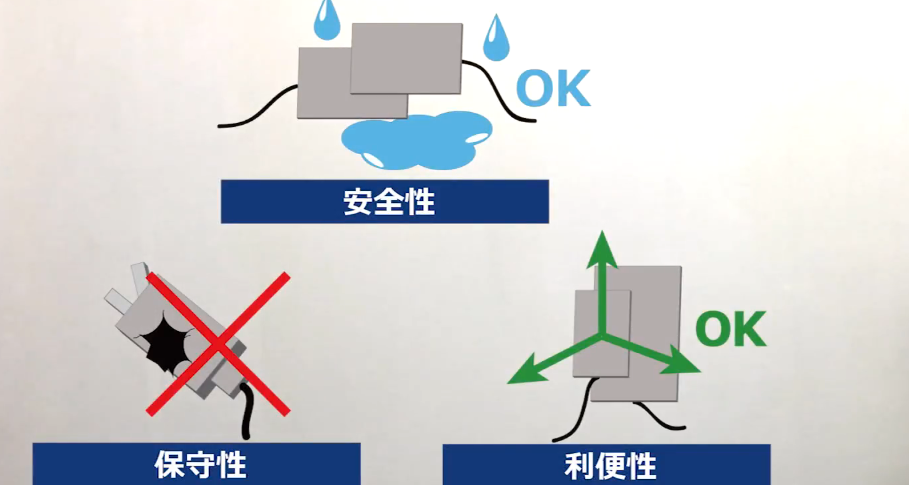

Digital Power Supply AC/DC BDG Series By digital power supply system, it can be change and monitor output voltage and more, with software. We do not have to change external circuit !! |