PALLETS Channel

Xilinx FPGA および Bellnixなどの電源部品の技術動画を配信中。

YouTube のチャンネルは

こちら

English Version

Click here

Bellnixはこちら

|

はじめて Xilinx 社 Vivado® Design Suite を使用する方へ |

|

Xilinx 社 開発ツール 概要 ・4つのHW設計ツール ・Vivado® Design Suite 、SDK、HLS、SDSoC™ |

|

Vivado® Design Suite 使い方 ① プロジェクト作成 ・FPGA の型式や評価ボードを指定し、プロジェクトの作成方法を紹介 |

|

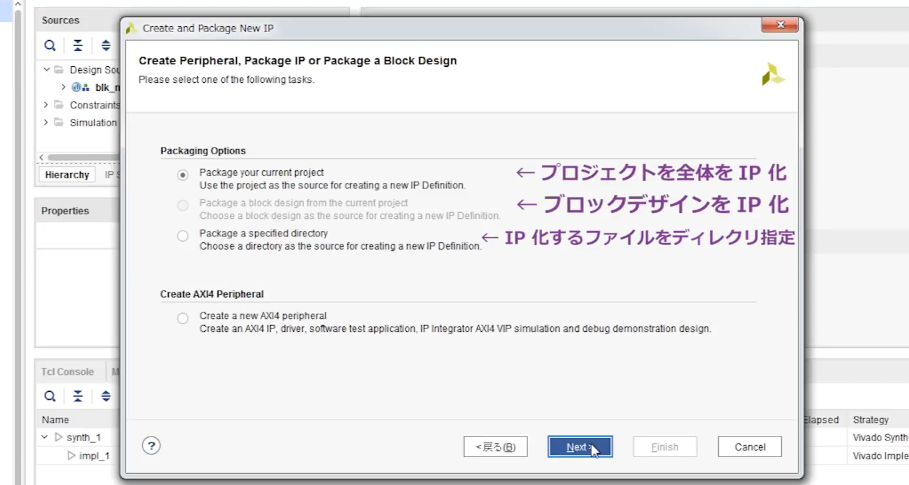

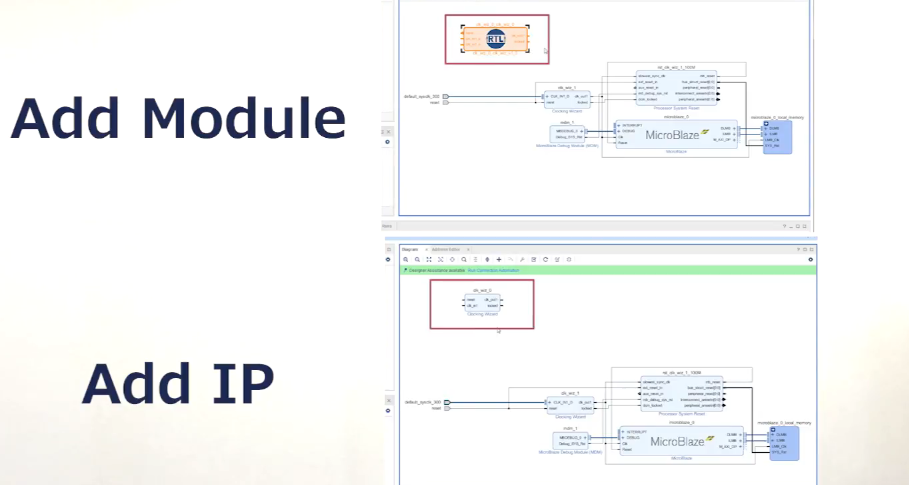

Vivado® Design Suite 使い方 ② IP 生成 ・IP の生成方法 と RTL をIP 化する方法を紹介 |

|

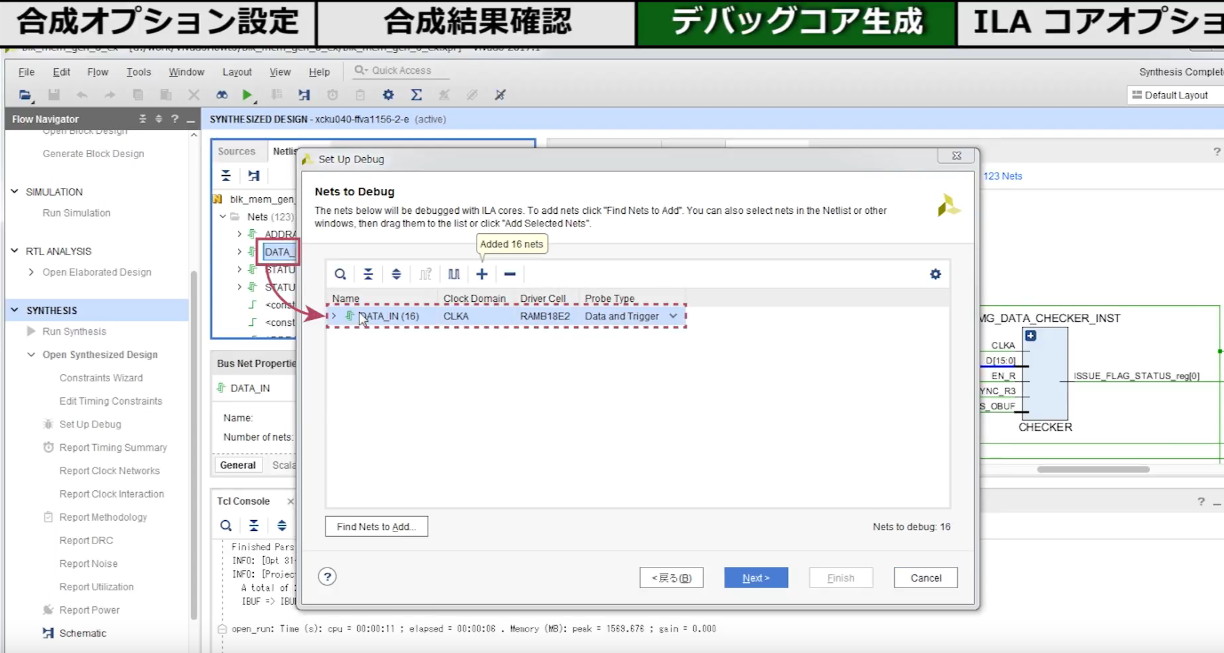

Vivado® Design Suite 使い方 ③ 合成とデバッグコア生成 ・論理合成オプション設定方法 ・RTL 記述なしでのデバッグコア生成方法 |

|

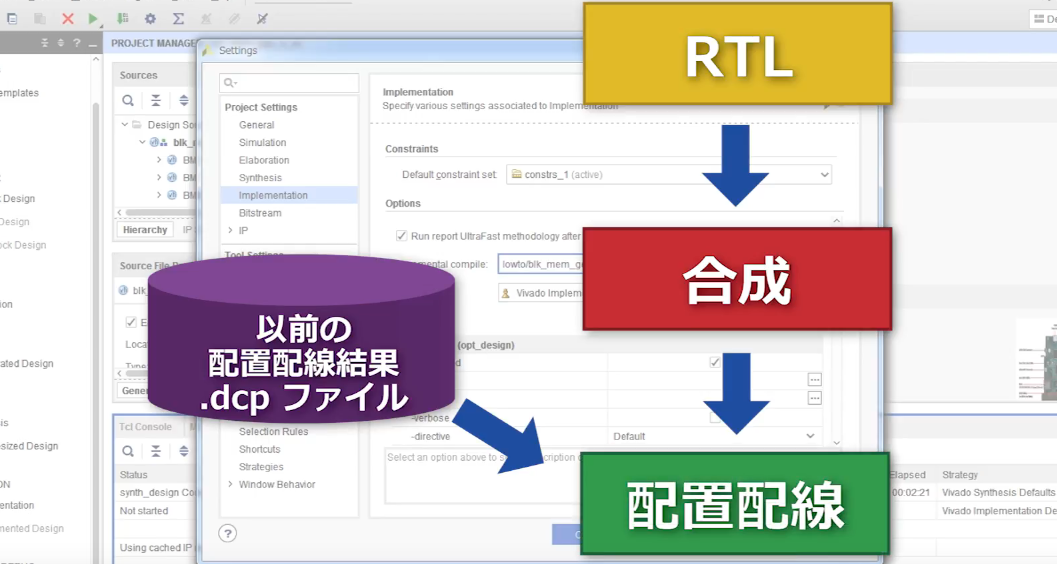

Vivado® Design Suite 使い方 ④ 配置配線 ・インクリメンタルコンパイル紹介 ・配置配線オプション設定方法紹介 |

|

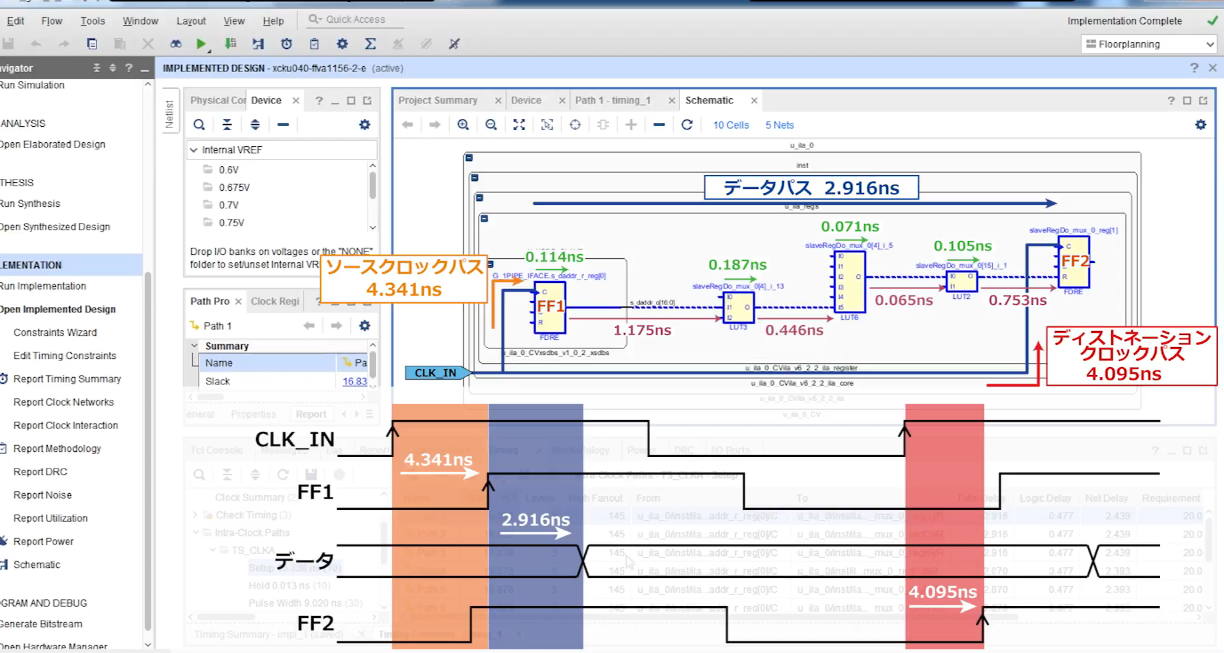

Vivado® Design Suite 使い方 ⑤ タイミングレポート ・タイミングレポート出力方法 |

|

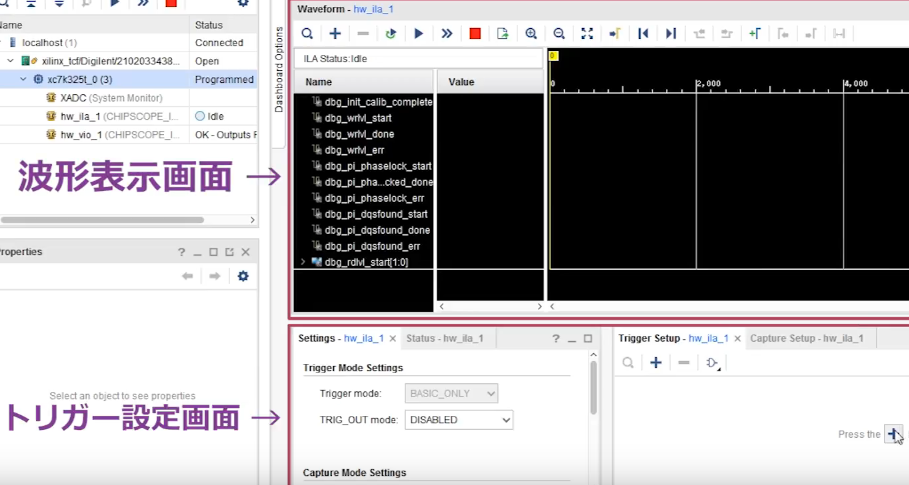

Vivado® Design Suite 使い方 ⑥ 書込みとデバッグ ・FPGAへの書き込みファイルの生成と書き込み方法 ・FPGA内部動作を確認するデバッグ方法紹介 |

|

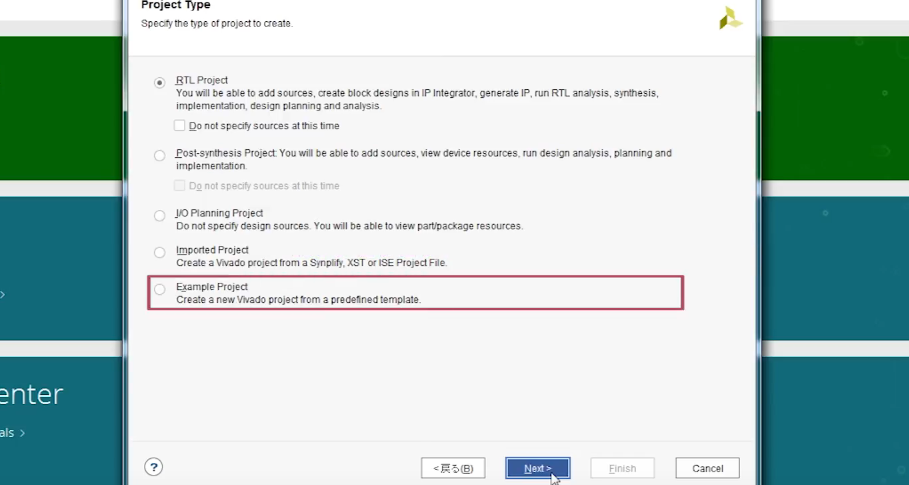

Example Design 生成方法 ・サンプルデザイン生成方法紹介(デバッグ時に使用) |

|

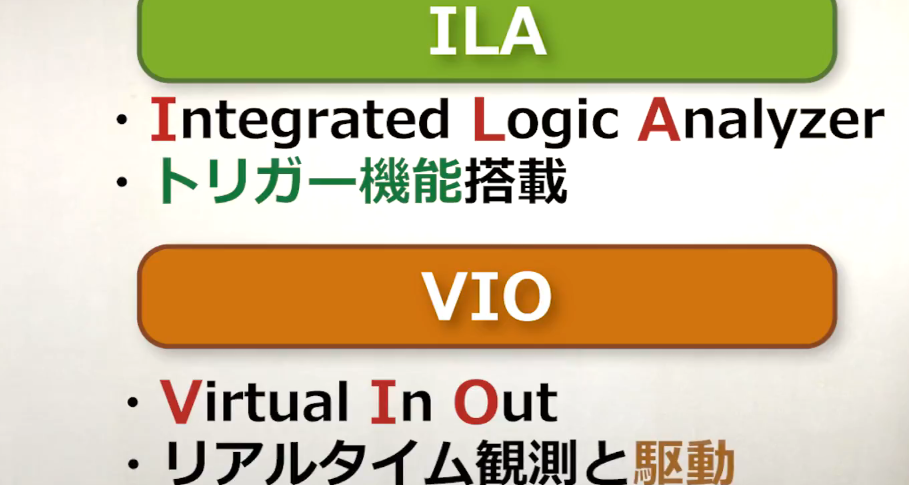

デバッグIP ILA/VIO の使い方 ・デバッグ時に有効なILA とVIO 2つのIP紹介 |

|

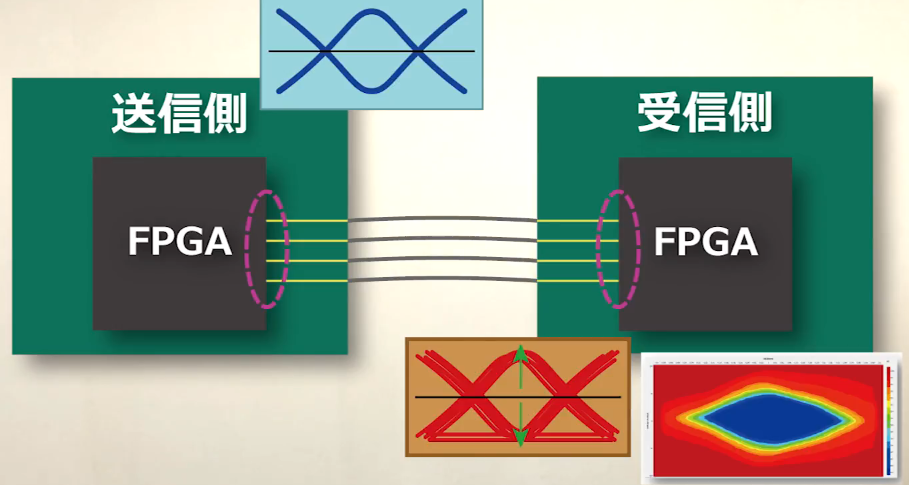

IBERT 使い方 ・トランシーバ用のデバッグIPで送信側、受信側設定出来ます |

|

Xilinx 社 製品 回路図作成時に見ておきたい動画 |

|

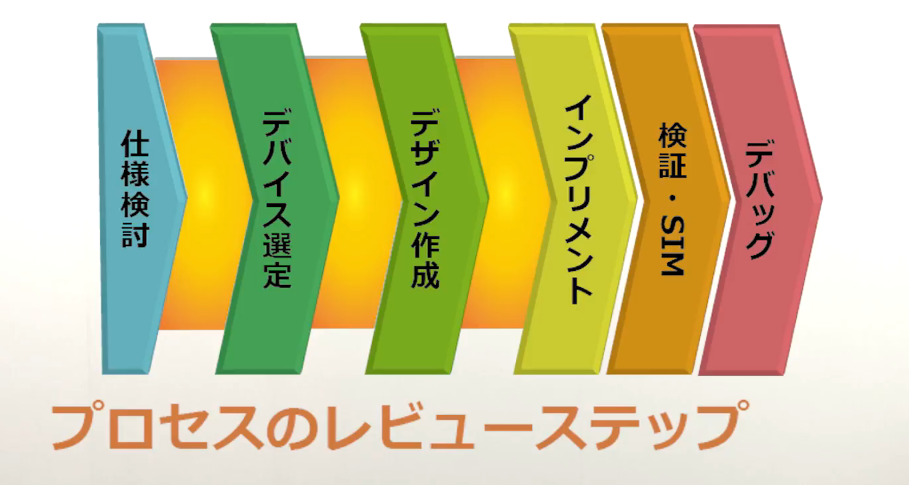

UltraFast™ 設計手法 概要 ・各プロセス毎にレビューステップを設けてる後戻り工数を削減する手法 |

|

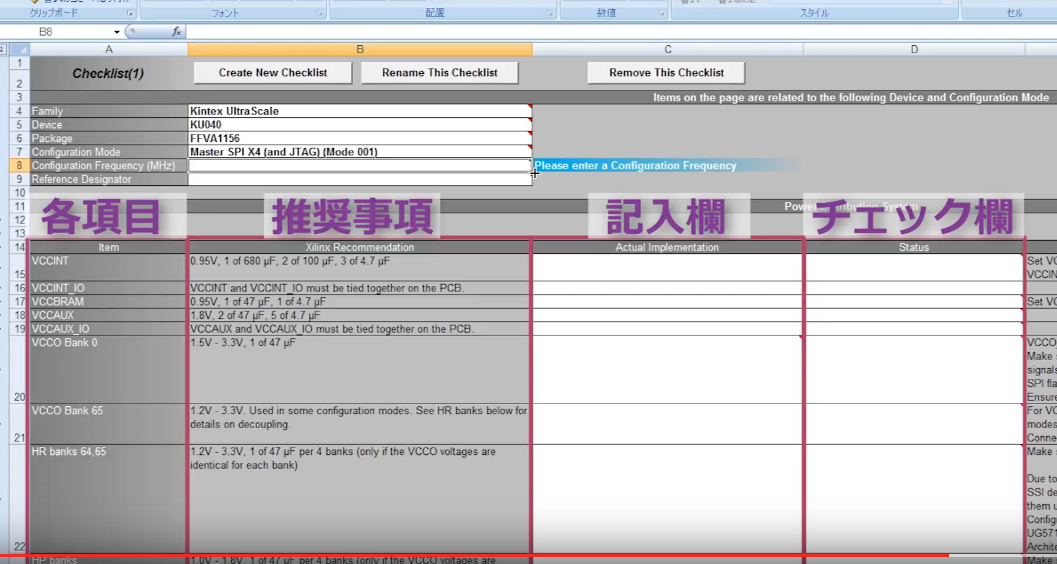

UltraFast™ 設計手法 回路図チェックリスト ・ピン処理等をまとめたチェックシートのダウンロードと使用方法を紹介 |

|

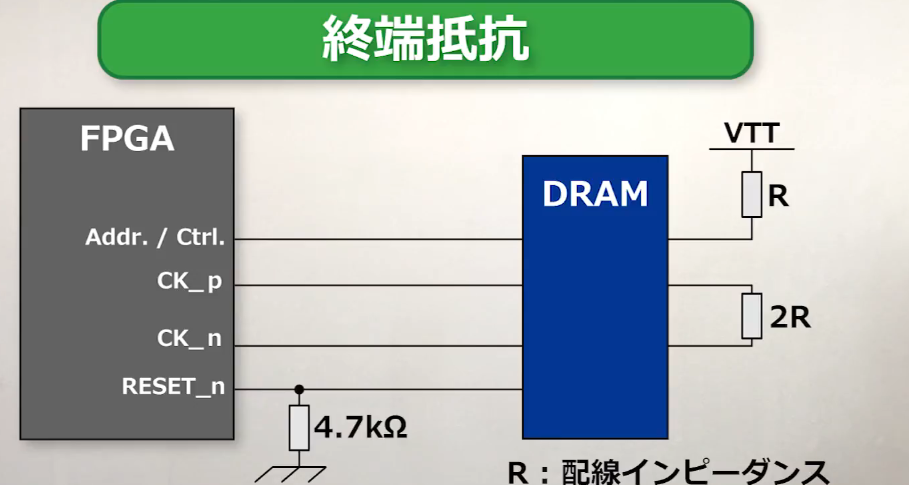

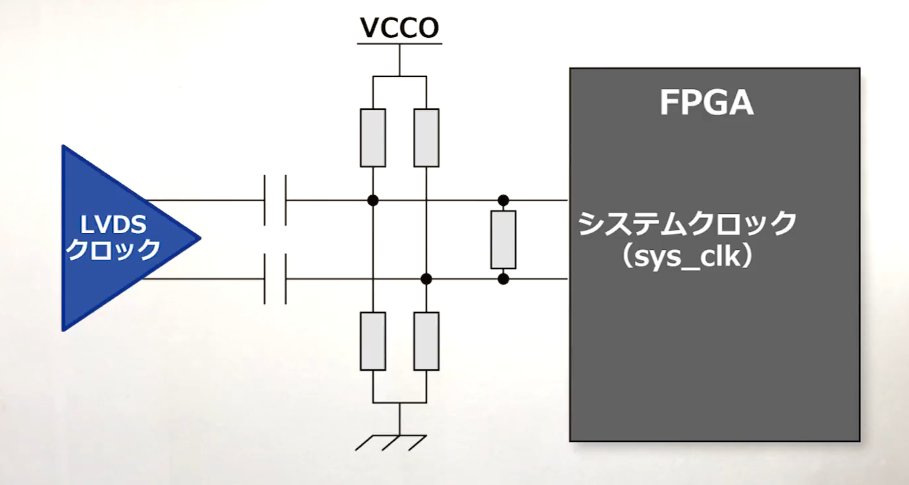

7シリーズ MIG 回路図注意点 ・7シリーズMIGに関するクロックと終端抵抗の質問をまとめました |

|

UltraScale™ シリーズ MIG 回路図注意点 ・UltraScale™ シリーズ MIGに関するクロックと終端抵抗の質問をまとめました |

|

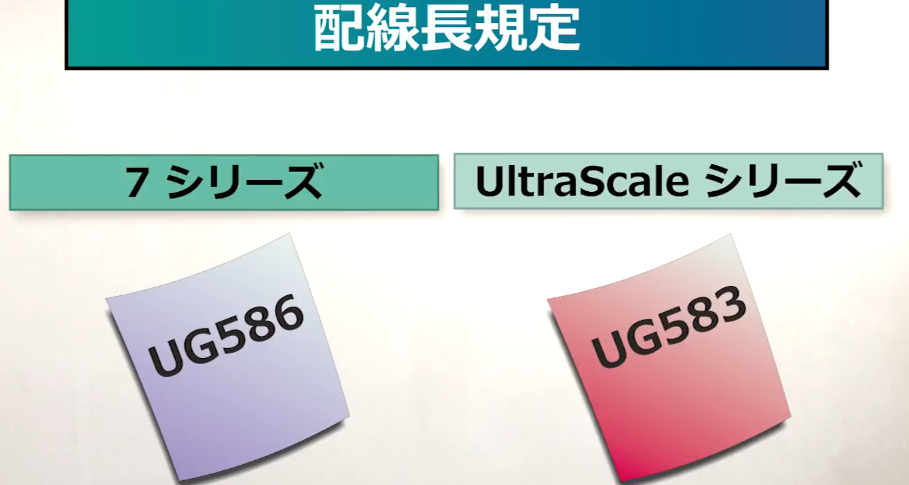

MIG 配線長の規定 ・配線長の規定を守ることで、安心・安全なインターフェースが確立 |

|

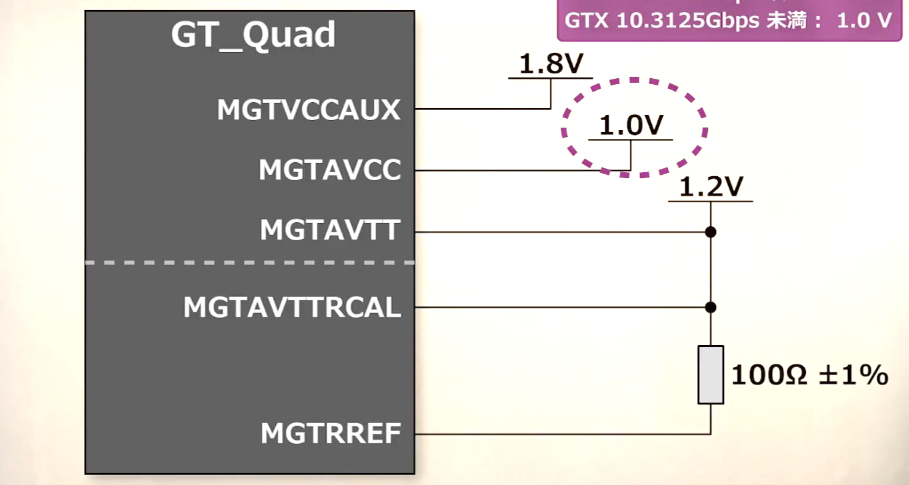

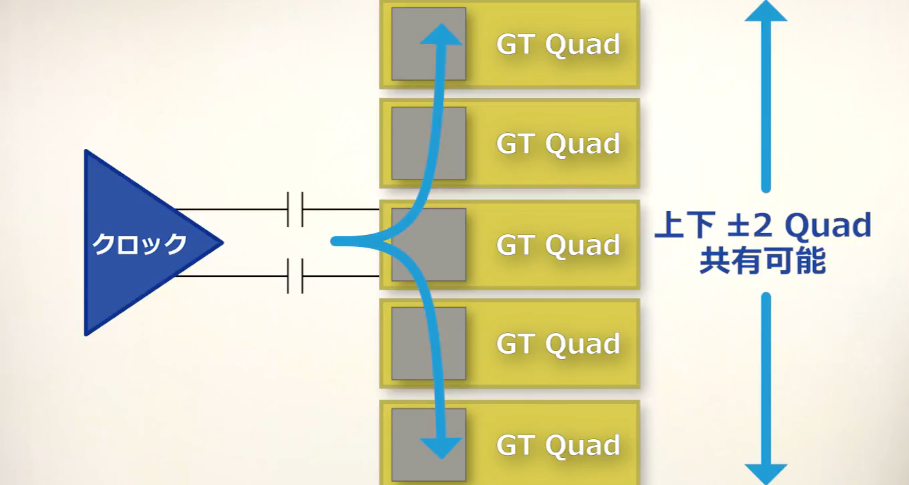

7 シリーズ トランシーバ 回路図注意点 ・7シリーズ トランシーバについて、 クロックの回路構成や共有幅、電源関連ピンの接続方法を紹介 |

|

UltraScale™ シリーズ トランシーバ 回路図注意点 ・UltraScale™ シリーズ トランシーバについて クロックの回路構成や共有幅、電源関連ピンの接続方法を紹介 |

|

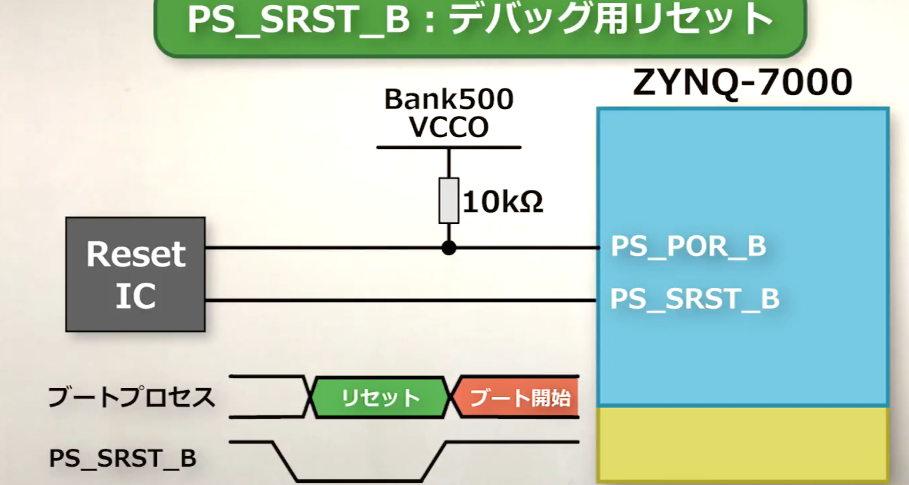

Zynq®-7000 All Programmable SoC PS 回路図注意点 ・Zynq®-7000 All Programmable SoC について PS 部分の、クロックとリセット信号の回路図注意点をまとめました |

|

Xilinx 社 製品 FAQ |

|

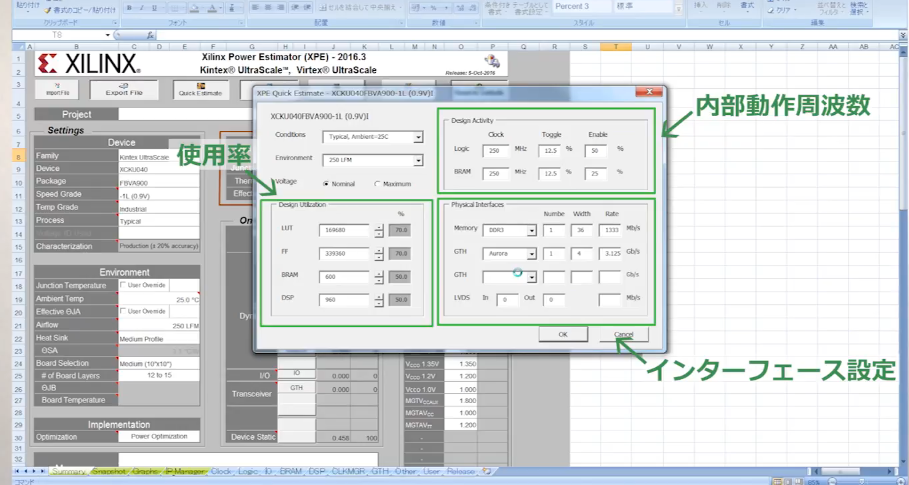

XPE 消費電力見積もりツール ・使用率入力などの概算見積もり方法 ・デザインを使用する詳細な見積もり方法紹介 |

|

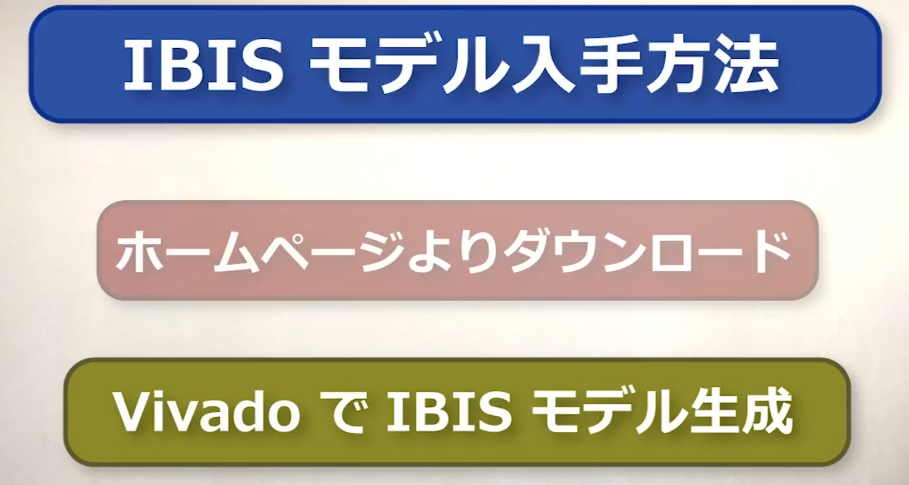

IBIS モデル入手方法 ・基板設計時に必要なIBIS モデルの入手方法を紹介 |

|

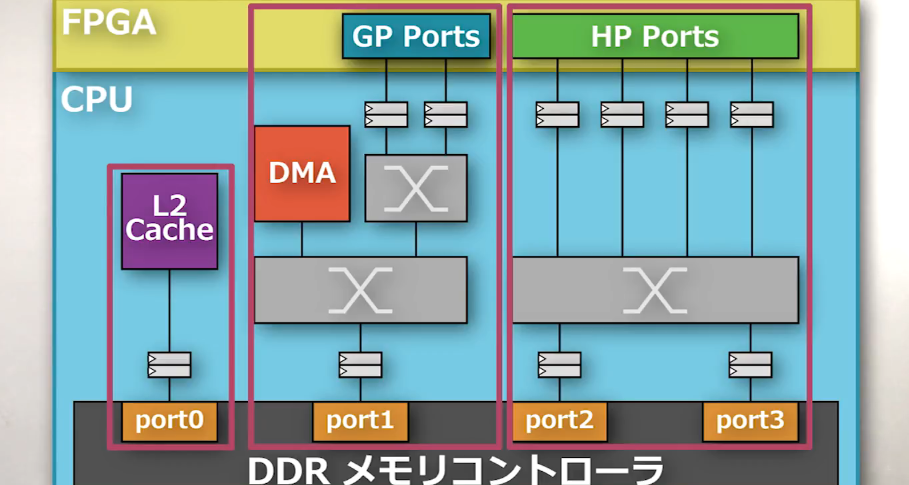

Zynq(R)-7000 All Programmable SoC DDR アービトレーション設定 ・DDR コントローラのアービトレーション設定を紹介 ・PL DDR からPS DDR への画像一括転送を効率的に |

|

評価ボードの初期動作確認手順 ・評価ボードの初期動作確認 |

|

Xilinx 社 Vivado® Design Suite ライセンスに関して |

|

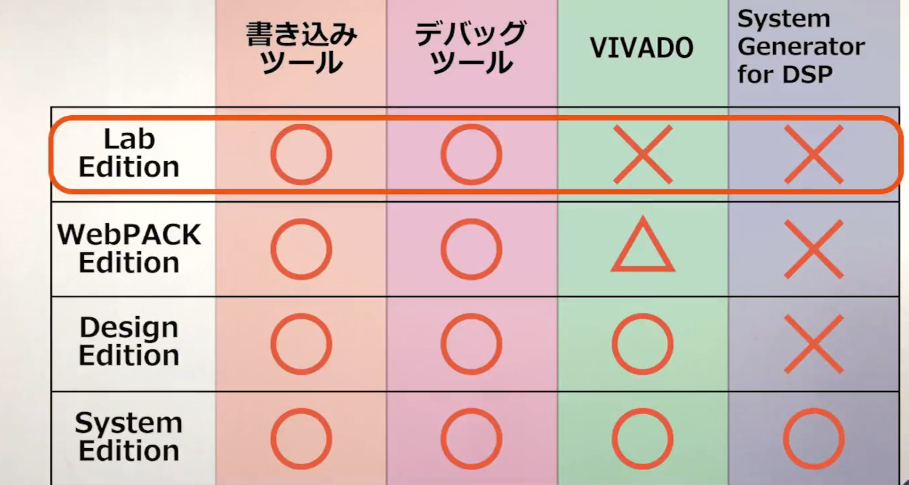

Vivado® Design Suite 紹介 Edition と License ・4つのEdition と2つのライセンス形態の特徴を紹介 |

|

ノードロックライセンス設定方法 ・ご使用のPCへのライセンス設定方法を紹介 |

|

フローティングライセンス設定方法 ・ご使用のサーバにライセンス設定方法 |

|

ライセンス FAQ ・Vivado® Design Suite のライセンス設定について よくある質問をまとめました |

|

Xilinx 社 Vivado® Design Suite 2017.1 新機能紹介 |

|

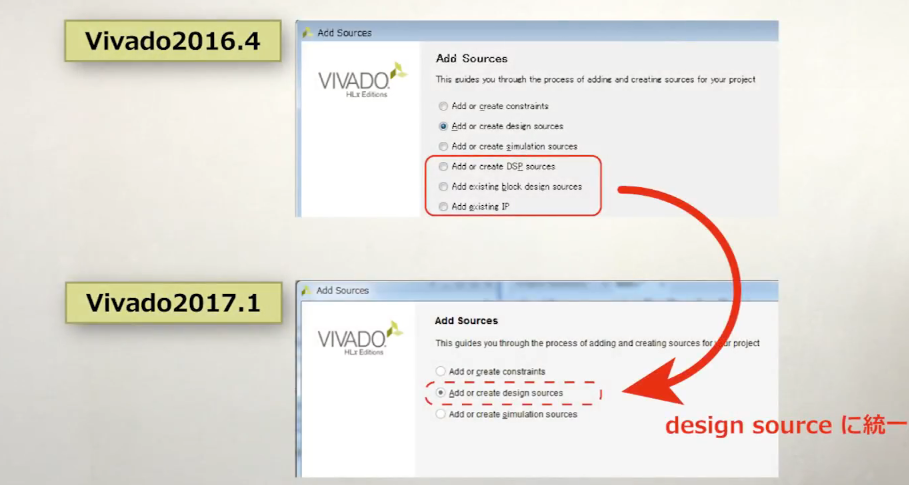

① 開発環境アップデート ・64bit OS対応 ・コメントアウト文字色変更可能 |

|

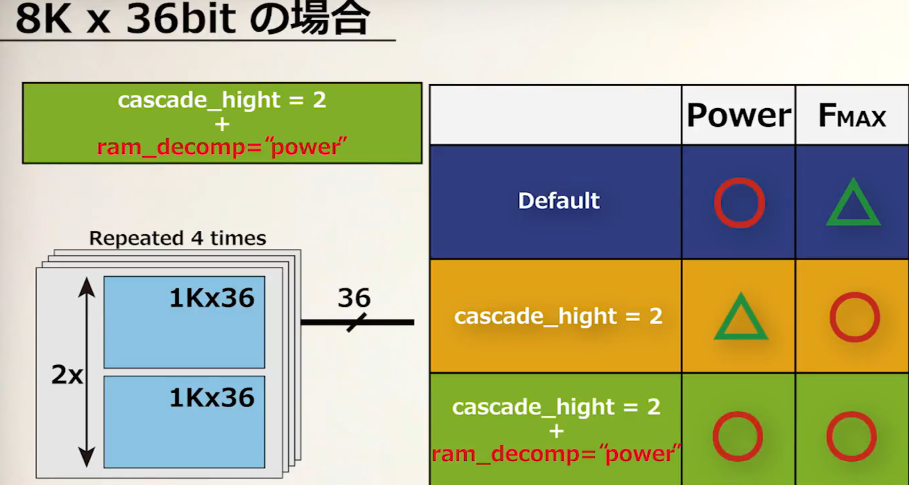

② 合成・配置配線機能アップデート ・合成と配置配線のアップデート点を紹介 |

|

③ IP 関連アップデート ・IP に関するアップデート点を紹介 |

|

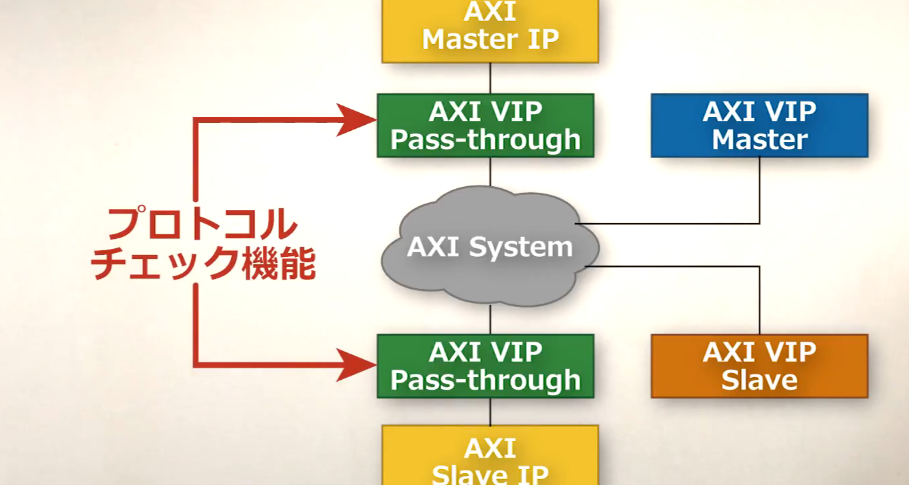

④ 新規 AXI Verification IP 紹介 ・新登場のAXI Verification IP を紹介 |

|

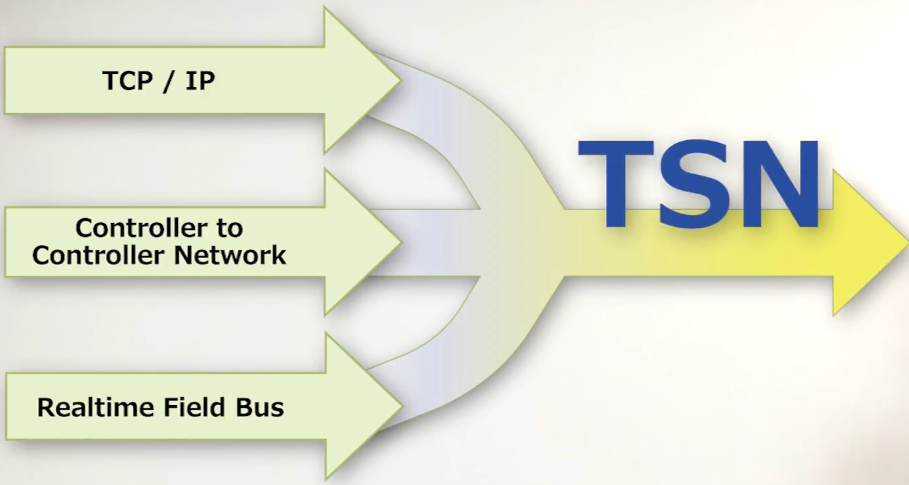

⑤ 新規 TSN IP 紹介 ・新登場のTSN (Time Sensitive Network) IP を紹介 |

|

Xilinx 社 製品紹介 |

|

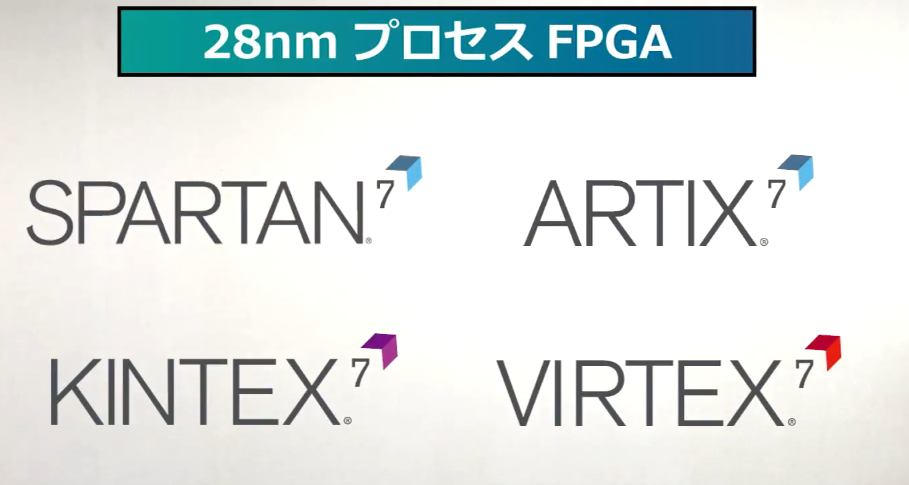

7 シリーズ FPGA 紹介 ・新製品Spartan-7 の最新情報あり |

|

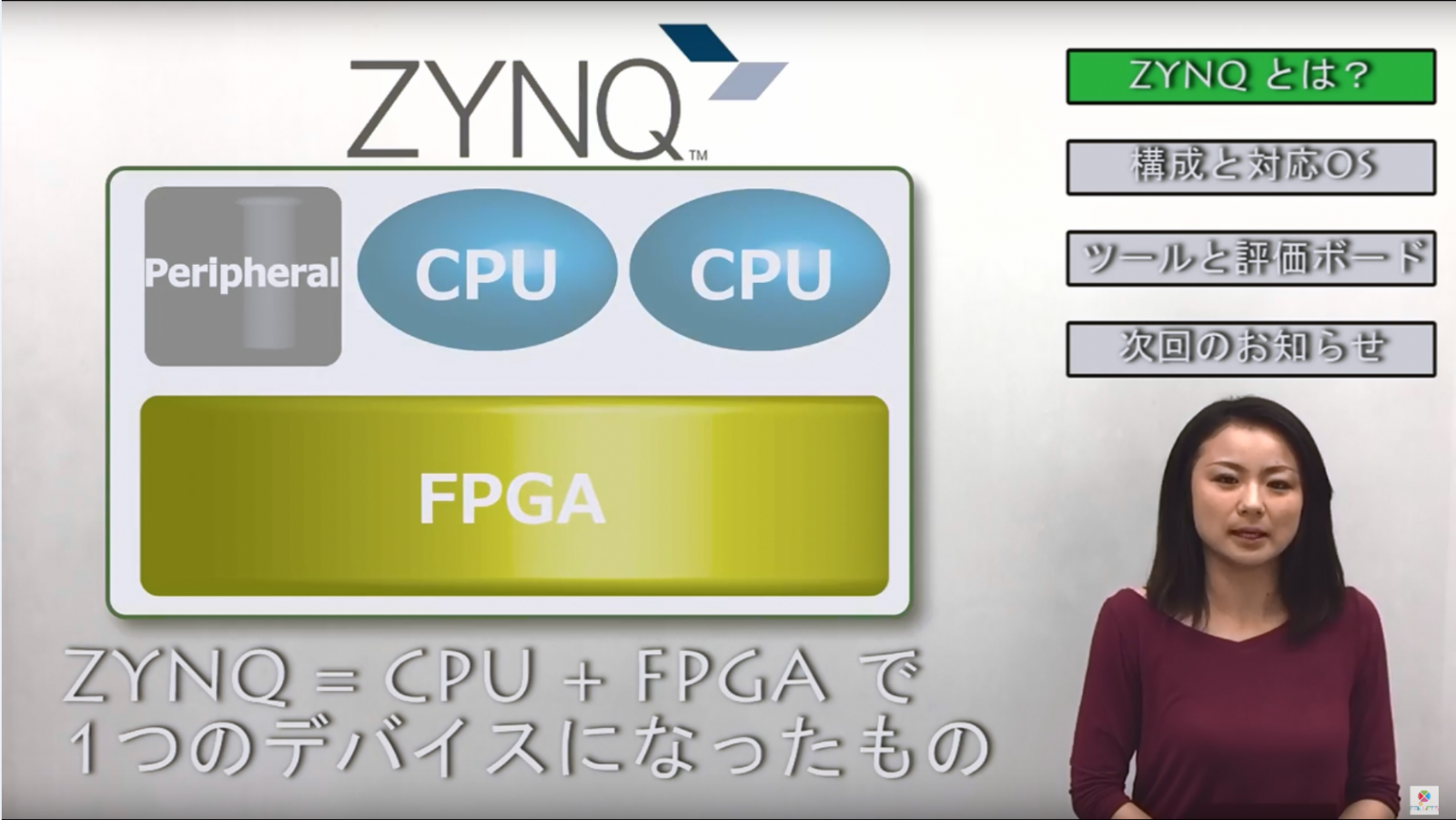

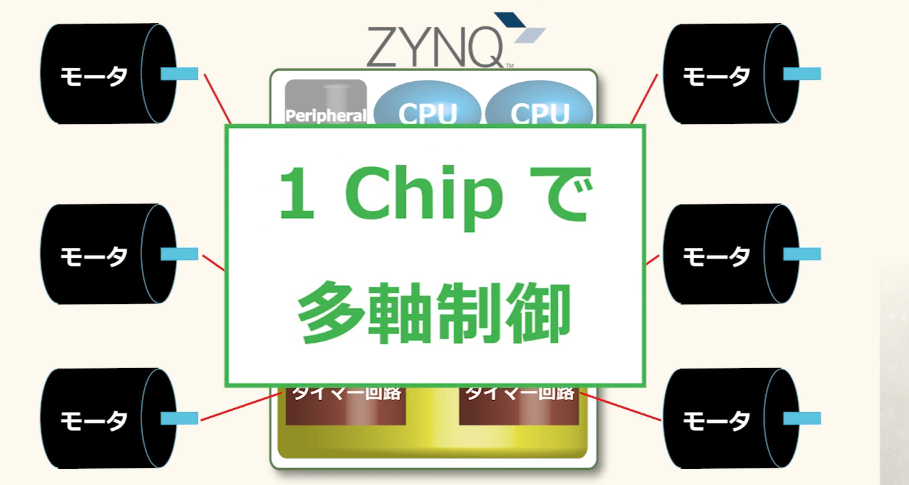

Zynq®-7000 All Programmable SoC 紹介 ・Zynq®-7000 All Programmable SoC概要 |

|

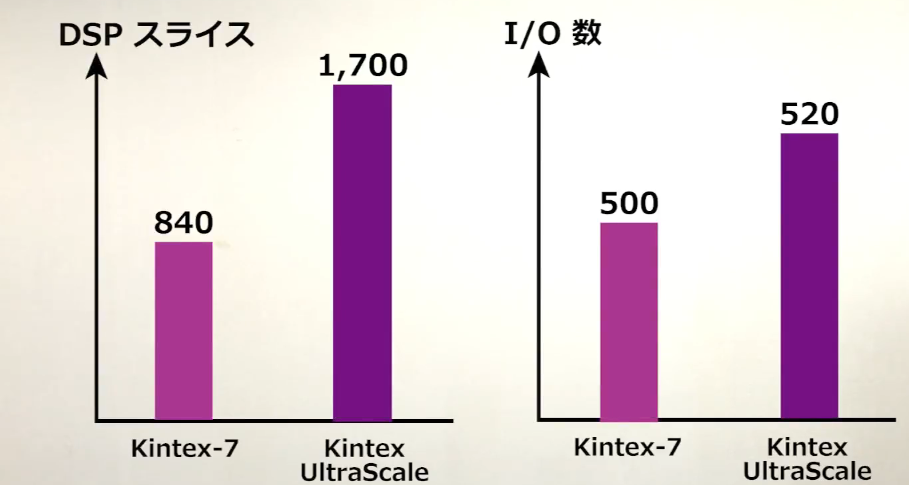

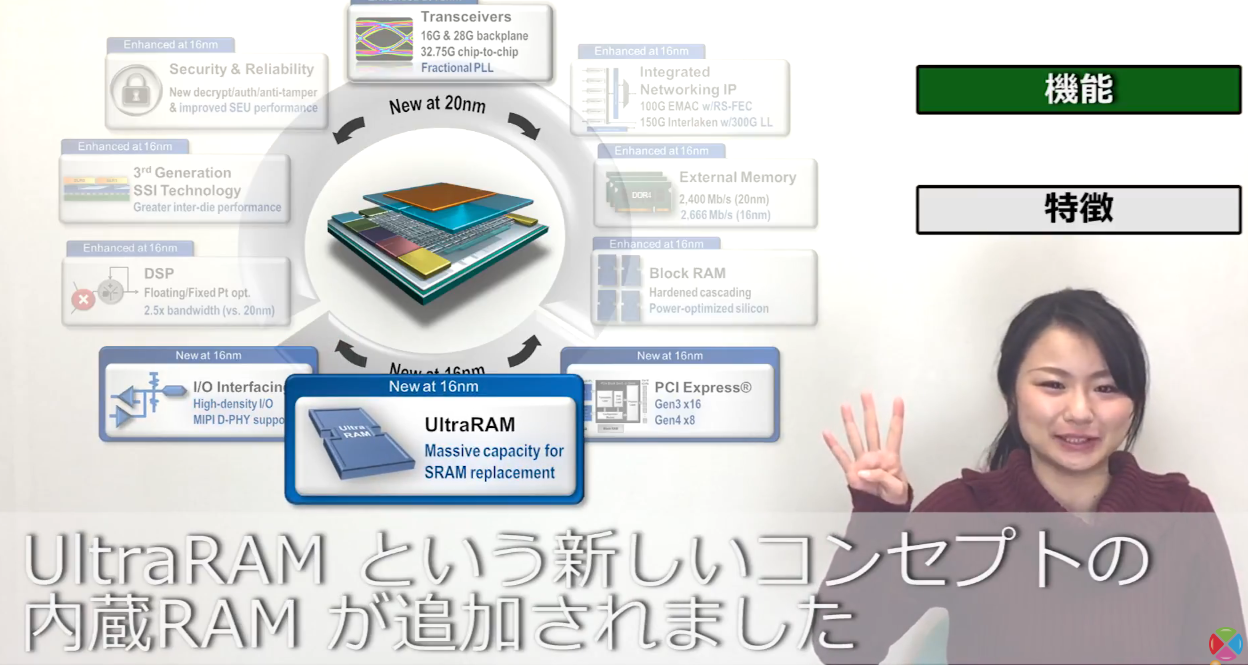

UltraScale™ FPGA 紹介 ・UltraScale™ シリーズ概要 |

|

UltraScale+™ FPGA 紹介 UltraScale+™ シリーズ概要 |

|

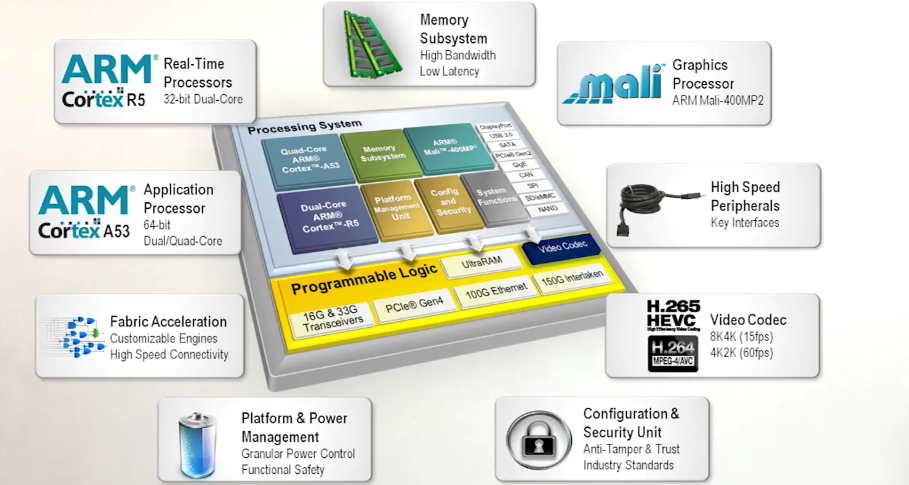

Zynq® UltraScale+™ MPSoC 概要 ・Zynq UltraScale+™ MPSoC 概要 |

|

Xilinx 社 Zynq® シリーズ動画 |

|

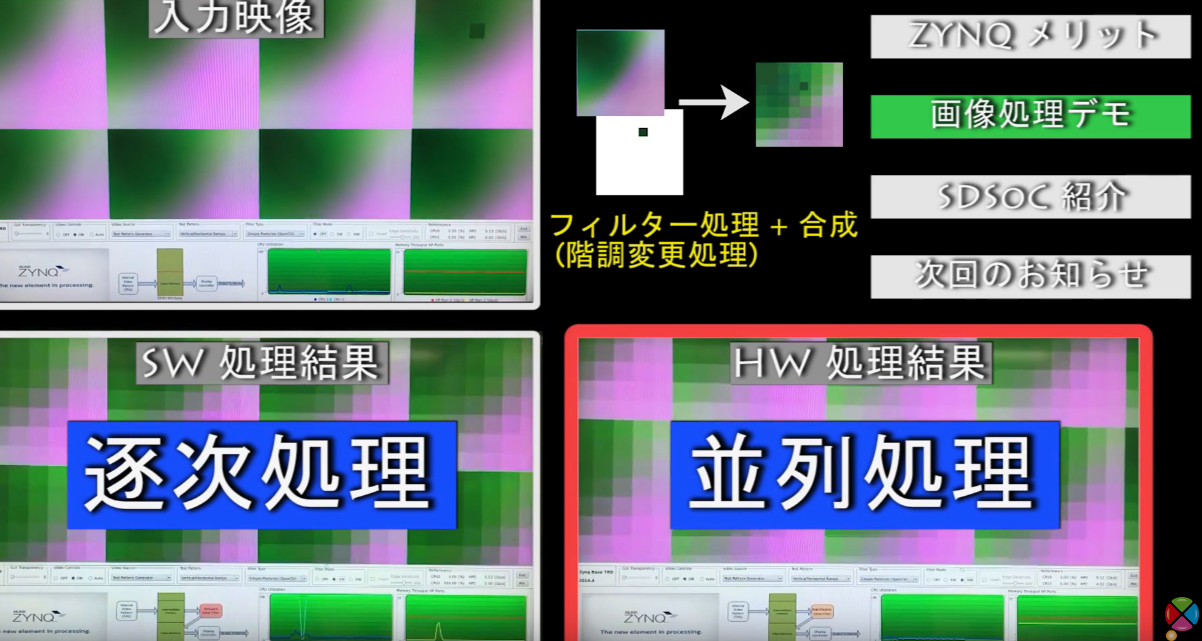

HW アクセラレーション ・ソフトウェア処理の一部をハードウェアで構築することで、 皆様の悩みが解消されます |

|

はじめてのZynq®-7000 All Programmable SoC (菊地様 対談) Zynq®-7000 All Programmable SoC をはじめて 使用した方のインタビュー動画 |

|

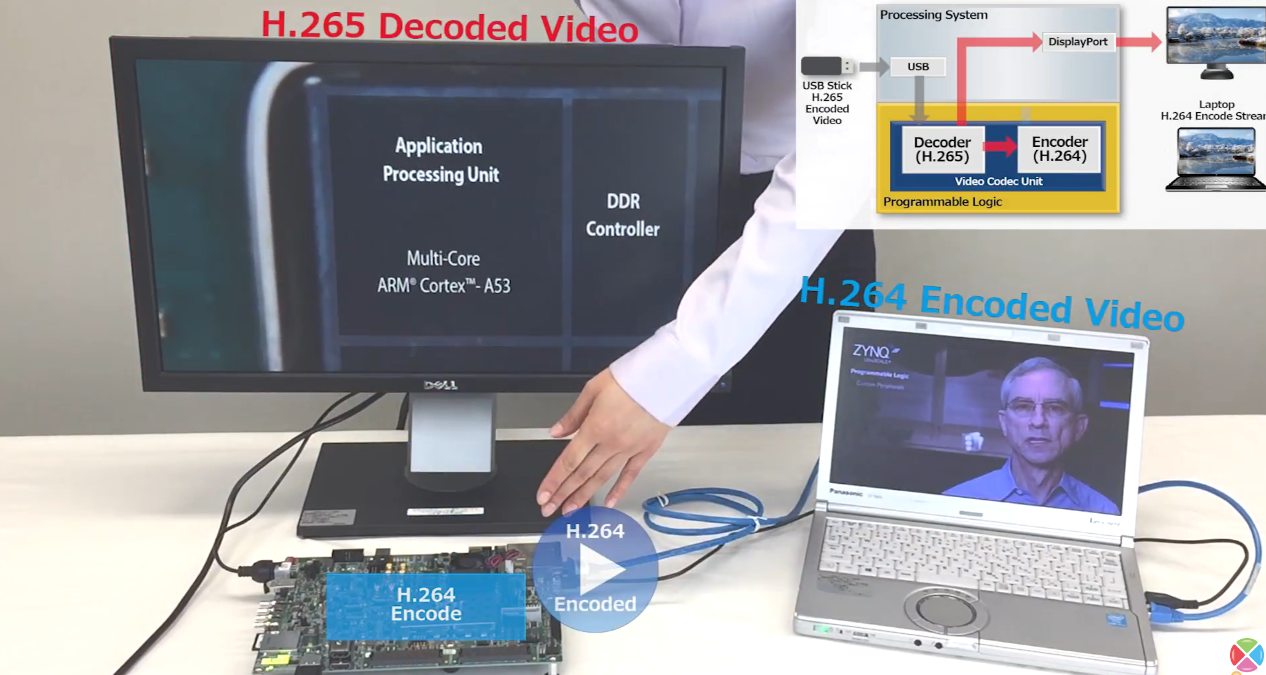

先行公開!H.265/H.264 ZCU106 デモンストレーション ・Video Codec Unit 搭載 Zynq® UltraScale+™ MPSoCを 使用したデモンストレーション |

|

Xilinx 社 reVISION Stack |

|

① 機械学習とは ・機械学習についておさらいからお話します |

|

② FPGA 機械学習のメリット ・機械学習をFPGA に実装するメリットを紹介 |

Bellnix 社 製品紹介 |

|

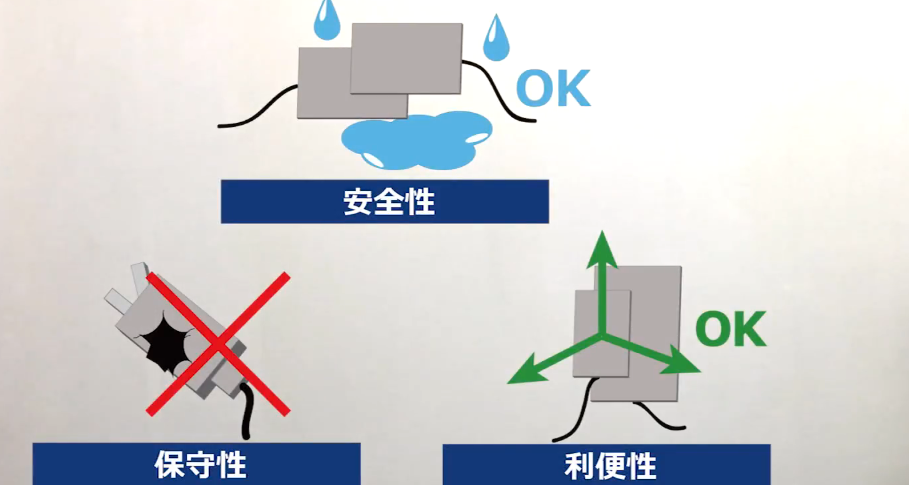

ワイヤレス給電システム紹介 独自開発のトランス形状により、位置ズレに対しても、高い電源変換効率を実現 |

|

デジタル電源 AC/DC紹介 BDGシリーズ デジタルAC/DC 電源であるBDG シリーズを、開発者のインタビューとデモを交えて紹介 セミカスタム電源の柔軟性に加え、デジタル電源のメリットを生かし、 多種多様な電源要求に応えることが可能 |